如何选择合适的电源模块为FPGA供电

现场可编程门阵列(FPGA)是可以包括数千个典型的、可编程逻辑单元.一个由线和可编程开关的矩阵与单独的逻辑单元互连.典型的设计包括指定每个单元的简单逻辑功能和选择性地关闭互连矩阵中的开关.

FPGA主要用于原型IC系统.当设计完成后,设计人员可以将逻辑转换为以更高速度工作的硬连接线IC.为了能正常工作,FPGA必须采用适当的电源管理技术.

FPGA有哪些供电要求?

FPGA的电源取决于内部电路的要求.FPGA有三个要配置元素:可配置逻辑块(CLB),I/O块(IOB)及其相互连接(见图).CLB提供功能性逻辑元素.IOB提供封装引脚和内部信号线之间的接口.可编程相互连接资源提供布线途径以连接CLB和IOB的输入和输出至合适的网络.施加于CLB(或核心)的电压被称为VCCINT.VCCO为IOB的供电电压.一些FPGA有被称为VCCAUX的另外一个电压输入.

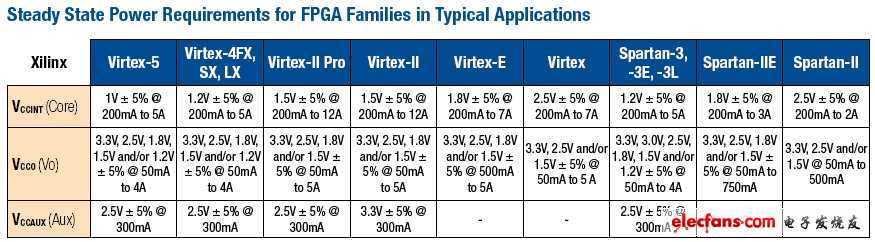

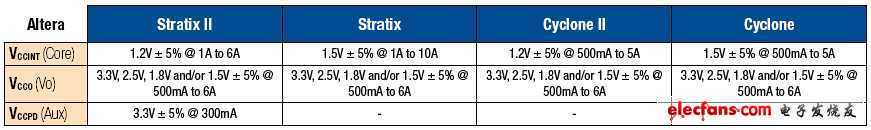

VCCINT的典型电压和电路取值如何?

典型的电压为1.2 V、1.5 V、1.8 V、2.5 V和3V,电流达12A.CLB数越大,电压越小而电流越高.此外,VCCINT应该单调上升,不允许有下降.

VCCO的典型电压和电路取值如何?

最常见的VCCO电压为1.2 V、1.5 V、1.8 V、2.5 V、3. 3 V,在以前的系统中甚至为5V.电流范围在1~20 A之间.

VCCAUX有哪些供电要求?

典型的辅助电压VCCAUX为3.3 V或2.5 V.它对FPGA中有严格时间要求的资源进行供电,所以它很容易受电源噪声的影响.除非VCCO不产生过大的噪声,VCCAUX可以与VCCO共用电源层.

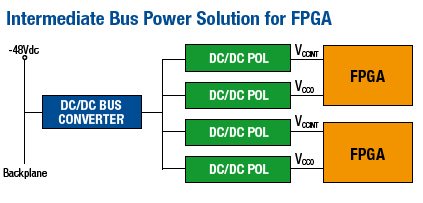

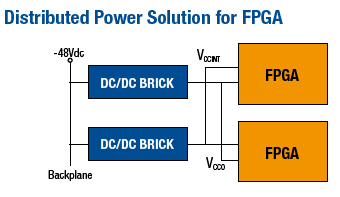

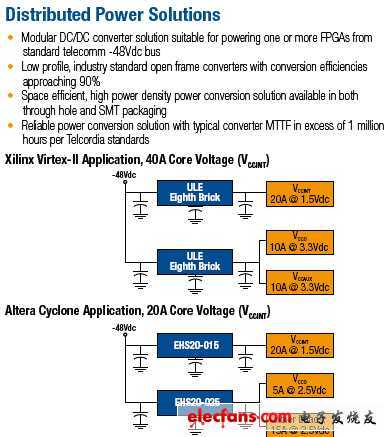

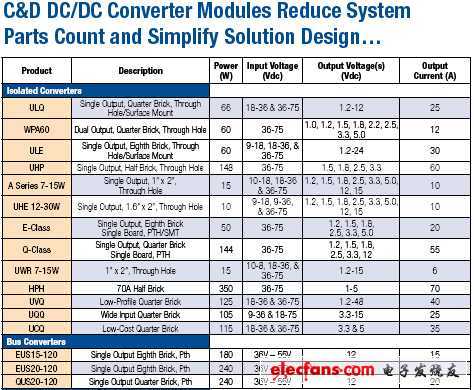

什么类型的电源资源可以被用于FPGA?

FPGA电源要求包括电压输出在1.2 V~5 V之间,电流输出大几十毫安到几安培之间.三种可能的解决方案为低漏失(LDO)线性整流电路、开关模式变压器以及开关模式电源模组.最终的选择取决于系统、成本和面市时间要求.

LDO有哪些优势?

如果板空间有保证,低输出噪声很重要,或者系统要求对输入和瞬态现象快速响应,就应该采用LDO整流器.LDO提供了中低输出电流.输入电容器通常会切断输入至LDO的阻抗和噪声.LDO还要求在输出侧有一个电容器,以处理系统瞬态现象并提供稳定性.双输出LDO还能同时向VCCINT和VCCO供电.

开关模式变压器有哪些优势?

当设计效率非常关键且系统要求大输出电流时,开关模式变压器具有优势.开关电源提供比LDO更高的效率,但其开关特性使其对噪声更敏感.与LDO不同,开关模式变压器需要使用电感器,而且可能需要变压器进行DC-DC转换.

哪些因素决定了FPGA的功耗?

CLB的功耗包括如所用CLB逻辑单元数/RAM块数的内部资源、工作时钟频率、切换率,布线和I/O功率.对于I/O功耗,影响因素包括输出类型、工作时钟频率、以及输出的信号翻转个数以及输出负载.实际功耗取决于特定的系统设计FPGA电源的斜升时间(ramp-time)要求有哪些?

为确保供电,核心电压VCCINT校正时间必须在一定范围内.对于一些FPGA,过大的校正时间会产生更长时间的供电电流,由于在变压器启通treash-old中VCCINT需要更长时间.开启校正时间长会引起热压力,如果电源向FPGA提供大电流.一些DC/DC变压器提供可调节软启动,允许通过一个外部电容器控制校正时间.校正时间取决于FPGA制造商,典型取值在50~100ms.

一定要采用FPGA供电时序?

许多FPGA没有时序要求,所以VCCINT、VCCO和VCCAUX可以同时供电.当不可能如此时,上电电流可能略高.对于特定FPGA时序不同.对于一些FPGA,重要的同时施加VCCINT和VCCO.对另一些FPGA,上电可以任意顺序进行.在大多数情况下,习惯于在施加VCCO之前施加VCCINT.

FPGA存在涌流问题吗?

当VCCINT在06.~0.8 V之间时,对一些FPGA系统存在涌流.在这期间,功率变压器连续供电.人们不希望在应用中有迭返(Foldback)电流限制,由于这一部分降低了输出电压以限制电流.但是在电流限制电源解决方案中,一旦电路以超过设定额定电流的电源供电,电源限制了电流达到额定值.

好东西,支持下.

很好,支持一下

呵呵呵呵

不错哟。

谢谢分享,小编辛苦了

正是需要时啊,小编辛苦了

谢谢小编分享

路过,看看,看看

谢谢小编了

学习一下,正需要这方面的只是