在全编译时出现hold time问题,跪求大侠知道

时间:10-02

整理:3721RD

点击:

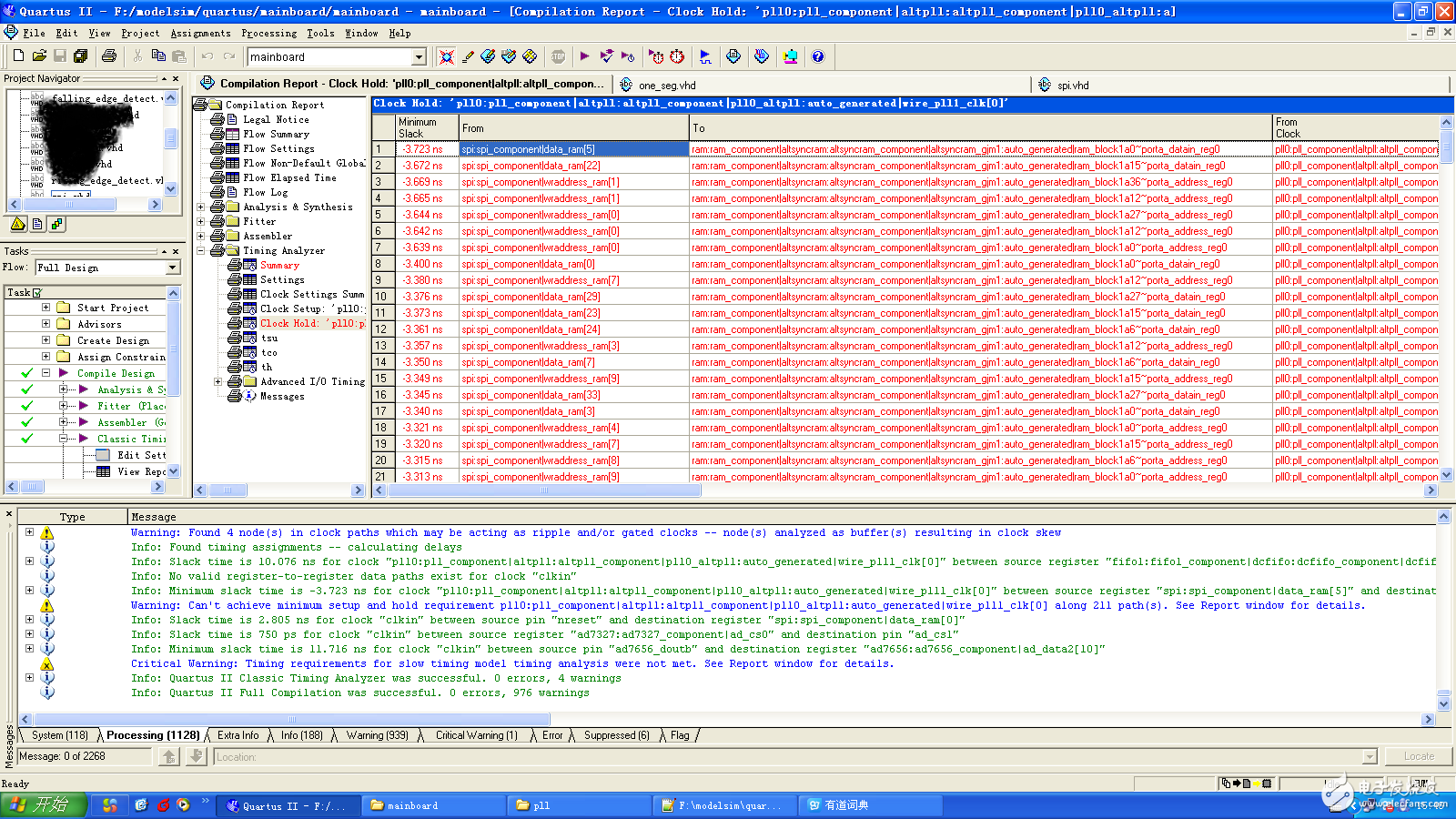

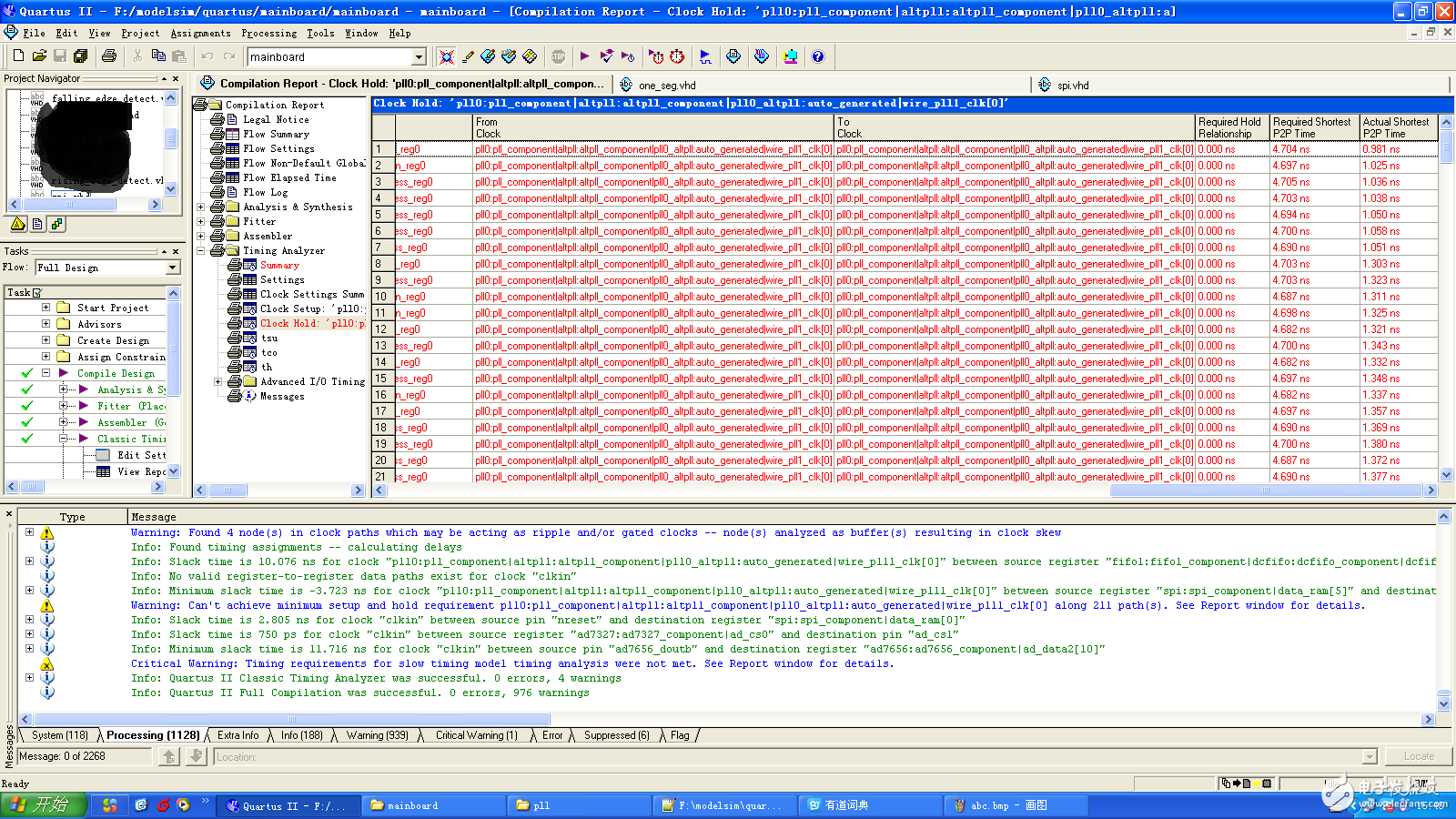

小弟最近在写FPGA程序,以前写过一些小程序,这次写的比较大的工程,用的是cyclone 3 的EP3C40的片子。在用这个片子时编译前还需要编写SDC文件,由于没有经验,就直接在class timming 内输入tsu、tco、th,在全编译时出现如附件中图片所示的warning,这个warning的原因都是和我用magic wizened生成的fifo和ram有关,然后自己也不知道该怎么弄了,不知哪位大侠知道?希望给与知道,不胜感激!

截图1

截图2

截图3

class timming 内输入tsu、tco、th是按照手册来写的吗?关于SDC我之前也没有做过,只是知道是时序约束文件,多多学习下

有太多的警告了 建议贴一下具体的实现方式

这个项目后来不做了,程序写了差不多了,遇到这个问题,我也就没有继续解决。最近一直在看关于时序约束的资料,看的是云里雾里的。

谢谢你的回复,这个项目现在停了,所以也就没有继续研究。知道自己在FPGA上还有很多欠缺,做这个项目能力还差些。最近一直在看时序约束方面的资料。看到你是高级工程师,想咨询一下,你对于时序约束方面是怎么学习的?有没有好的资料推荐一下。以前在学校感觉资料很多,只怕自己不去学习。现在工作发现遇到问题却没有太多资料可以查看。希望你可以提几点建议。谢谢啦!