《从算法设计到硬线逻辑的实现》中第十章练习6-在Verilog H...

时间:10-02

整理:3721RD

点击:

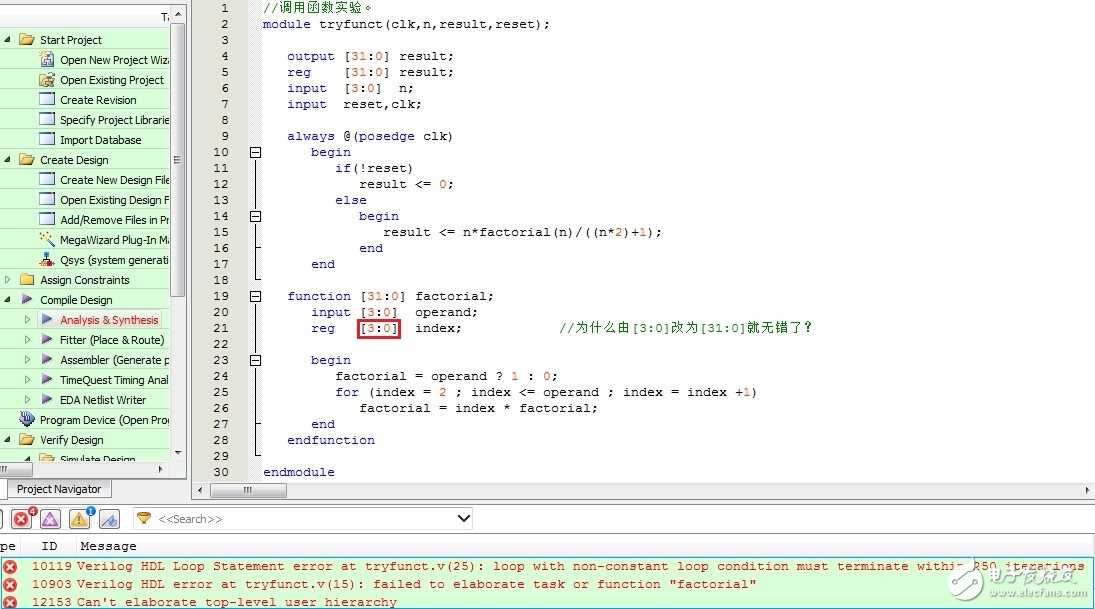

在做夏宇闻教材《从算法设计到硬线逻辑的实现》中第十章练习6-在Verilog HDL中使用函数

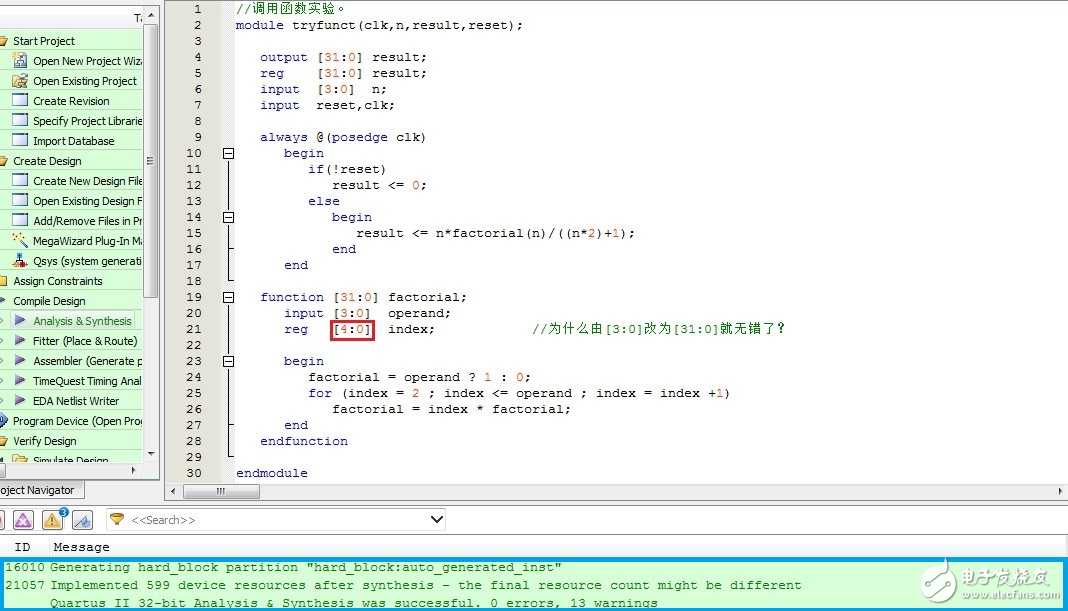

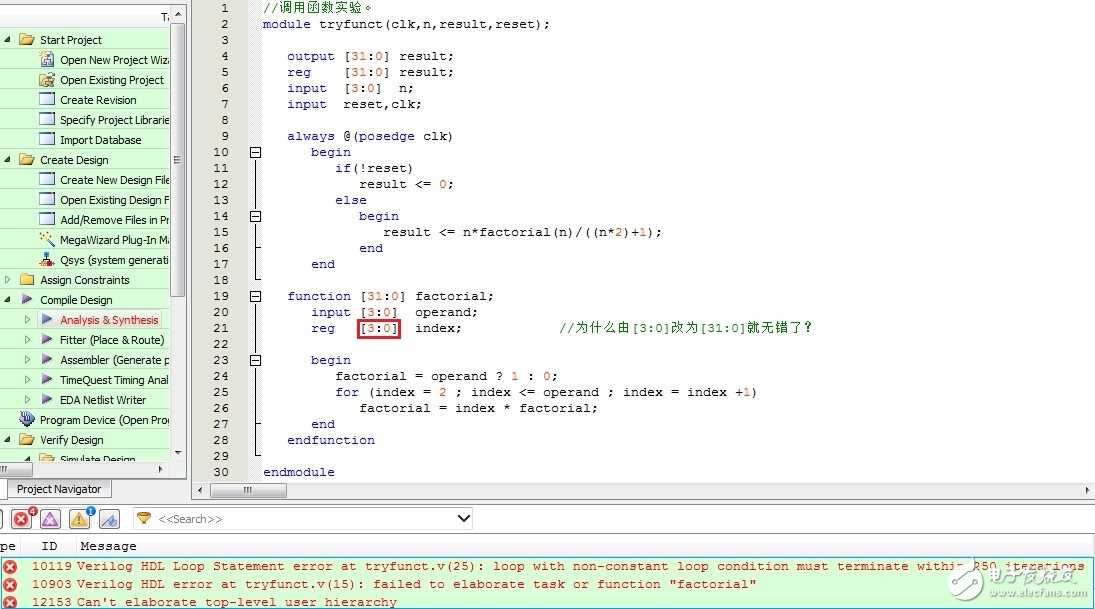

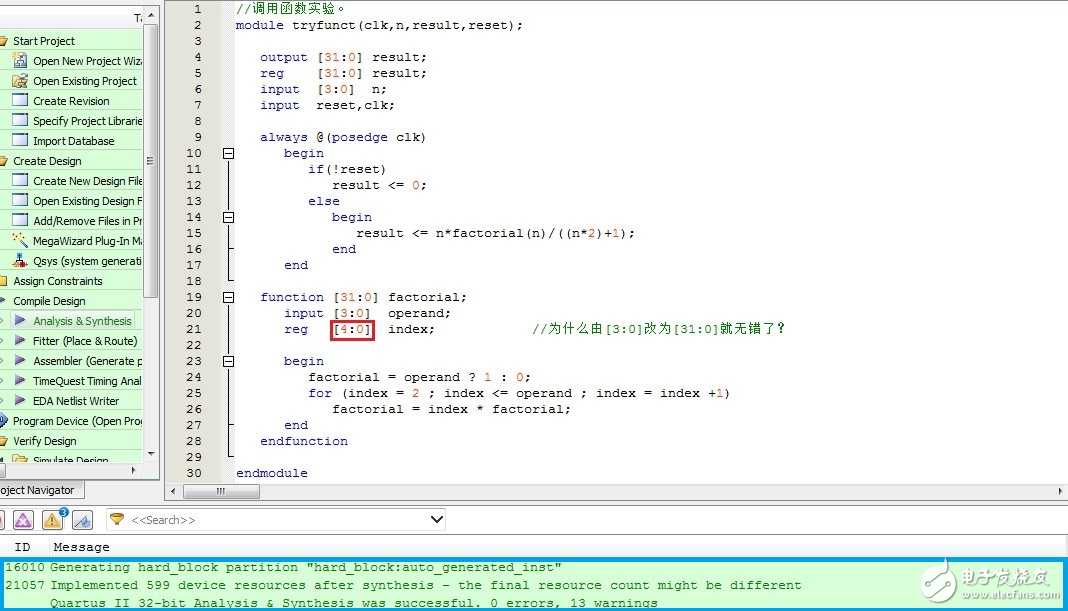

按原文编译总是出错,将[3:0]中的3改为大于3的值就没错了,如[4:0].为什么呢?

按原文编译总是出错,将[3:0]中的3改为大于3的值就没错了,如[4:0].为什么呢?

index被定义为寄存器类型,错误可能是因为你定义的位数小,位数变大了当然不会错误了

从报出的错误来看是因为这个循环中的终止条件不是常数,导致for循环在250次循环后终止。也是主要因为第一个程序的index和operand都是4位的,而把index变大后就可以判断终止条件是当operand为15时for循环终止。

楼上说的对,

3楼正解。