噪声估计(两个数相加和另一个数比较怎么实现)

时间:10-02

整理:3721RD

点击:

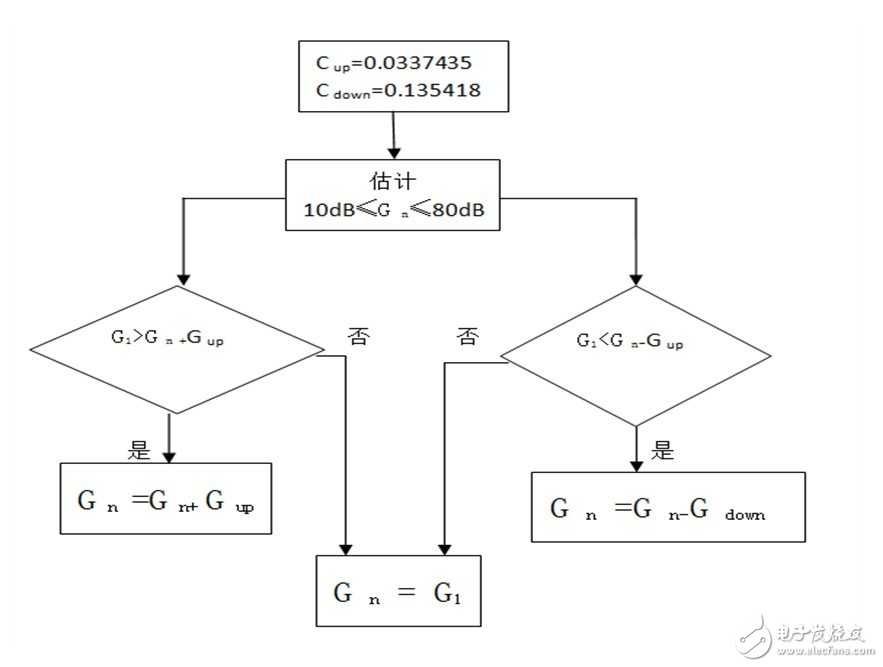

下面的算法怎么用verilog实现啊,主要用什么语句啊,初学fpga 不知道该如何下手。

我想应该用 if 语句 但是中间的那个加法 G1>Gn+Gup 怎么用verilog实现呢?其中数据格式都是32位,请大侠们帮帮忙,谢谢啦 下面是matlab代码

%noise estimate

function G_n=noise_est(gain,G_n)

global Cup Cdown

if gain>G_n+Cup

G_n=G_n+Cup;

else if gain 20

G_n=20;

end

我想应该用 if 语句 但是中间的那个加法 G1>Gn+Gup 怎么用verilog实现呢?其中数据格式都是32位,请大侠们帮帮忙,谢谢啦 下面是matlab代码

%noise estimate

function G_n=noise_est(gain,G_n)

global Cup Cdown

if gain>G_n+Cup

G_n=G_n+Cup;

else if gain 20

G_n=20;

end

verilog语言和c很相像,只是c是纯软件的,而verilog语言还要考虑寄存器等实际硬件。只要学习下很简单的,重在多多练习,多多使用。可以参考下附件中的 《Verilog HDL程序设计与实践》

http://yunpan.cn/QNFXb9bHWz2wa 访问密码 90c4