基于ADS和Matlab的超宽带低噪声放大器的频带选择性设计(论文)

时间:10-02

整理:3721RD

点击:

0 引言

随着无线通信技术的发展和广泛应用,频率的需求越来越高,带宽也越来越宽,使得传统的窄带系统已经无法满足大流量数据传输的需求,因此宽带无线通信电路设计成为研究热点。2002年2月14日,美国联邦通信委员会(FCC)正式立法开放3.1~10.6 GHz频段给UWB系统作免执照使用。UWB技术具有发射功率较低、占空比低和抗干扰等特点,被应用在无线电话会议、无线短距离数据传送等诸多领域[1-2]。然而在FCC开放的频谱中来自授权频带WLAN的信号对免执照使用的频段UWB存在很强的干扰。UWB信号是微弱信号(频谱密度为-41.3 dBm/MHz),可比拟噪声甚至比一些噪声的频谱密度更低,所以UWB信号不会对WLAN信号产生明显的影响[3]。考虑到这两种无线局域网的使用区域出现交叠,致使UWB信号在5~6 GHz频段内完全被WLAN信号所淹没的情况,许多文献都进行了深入的研究。文献[2]设计了一个带阻滤波器来滤除WLAN信号,然而这种方法不仅要求整个通频带平坦度要好,滤波器在截止频率处的衰减响应更加陡峭,而且滤波后产生极大损耗和相移。同样使用多个LNA累叠的方式[4],来放大各自频段的UWB信号,这种方法不但增加了设计的工作量而且增加了成本。文献[5]则是设计了多谐振负载网络来实现整个频带的选择性,在整个系统中实现了对WLAN信号的屏蔽。

对此,本文也采用这种实时放大与选择的工作方式,对多谐振负载网络进行更深入的研究与设计,提出更加优良的多谐振负载网络,实现优于各文献的频带选择性。鉴于此,设计一种具有频带自主选择性的超宽带放大器[6-7],使之既能屏蔽来自授权频带信号的干扰,又能同时放大UWB下边带(3.1~5 GHz)及上边带(6~10.6 GHz)的信号,成为本文研究的重点,而能实现这种频带选择性的多谐振负载网络的设计更是本文工作的重要核心。

1 电路设计

整个电路的设计主要包括具有频带选择性的多谐振负载网络设计和放大器结构设计两个部分。

1.1 具有频带选择性的多谐振负载网络

本文通过对谐振特性的研究,设计了一种全新的具有频带选择性的多谐振负载网络结构,如图2所示,它能更好地屏蔽来自授权频带信号的干扰,又能通过UWB下边带和上边带信号。

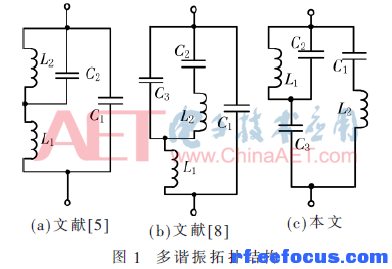

图1(a)、图1(b)和图1(c)分别展示了3种多谐振网络结构,这3种网络均可实现频带选择性。其中图1(a)是文献[5]提出的结构,两电容和两电感简洁而有效地实现了宽频带上的选择特性;图1(b)是文献[8]提出的双串联双并联结构,引入调谐电容C2作为网络优化元件,降低了多谐振网络对高电感值的依赖,提升了多谐振网络频带选择性能。图1(c)是本文所提出的结构,引入调谐电容C1的双串联双并联结构,不仅提升了频带选择性能,而且更加强了对WLAN信号的屏蔽作用。

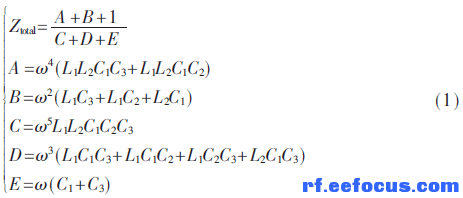

当频率从低到高时,受到电感扼流作用的影响,阻抗值是不断增加的。根据多谐振网络的拓扑结构,多谐振负载网络总的阻抗为:

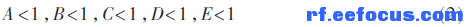

从式(1)可以看出,多谐振负载阻抗的分子项由角频率的偶次项组成,分母由奇次谐波分量构成。由于工作在吉赫兹频段,为了能对信号产生调谐作用,电感和电容的量级确定为纳亨级和皮法级。由此可知:

由于谐波分量次数越高其值越小,所以Ztotal的分子值大于分母值,当且仅当f=5.5 GHz即为有约束条件的极值点:

当频率为5 GHz和6 GHz处,阻抗值为10logZtotal=0 dB的间断点,此时开始出现衰减特征。由此可知:

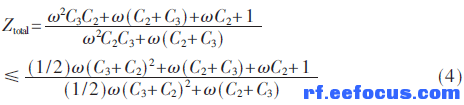

假设当C2=C3时,可得Ztotal,5 GHz=Ztotal,6 GHz。工作在最高频点10.6 GHz处,最大允许的负载网络的损耗为3 dB,即是:

可推导得C2<2/(2π×10.6×109)=30 pF。

通过仿真软件MATLAB进行编程仿真,C2初始值设定为30 pF。通过不断降低C2的值进行迭代运算,当C2=1.82 fF时,可得到本文提出的多谐振拓扑结构的最佳选择特性,这时L1=0.355 nH,L2=0.25 nH,C1=0.55 pF,C3=3.001 pF。

1.2 放大器结构设计

超宽带低噪声放大器是UWB无线接收机中的一个重要的模块,它必须在很宽的频带范围里提供足够高的增益和引入尽可能小的噪声,因此选择一个良好的电路拓扑结构来实现其性能要求是很重要的[9]。

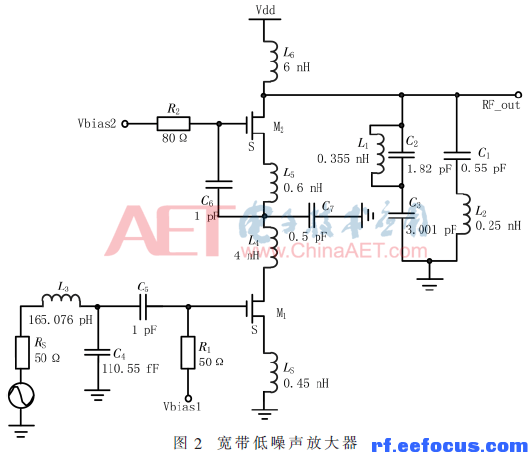

电感源极负反馈结构其实采用的是共源极的放大电路,它是低噪声放大器很常用的一种电路[10]。本文采用电感源极负反馈的共源共栅结构,同时引入电流复用结构,构建出完整的频带选择性的超宽带放大电路,如图2所示。在M1源极引入一串联电感,此电感在较高品质因数下几乎不引入噪声。在工作频率内,加载在M1栅极的电感与MOS管的等效电路中的输入回路中的电容恰好形成谐振,可实现输入阻抗匹配。由于两个晶体管M1和M2在同一条偏置电路上,电流的功耗即为原来的一半,因为高频信号首先全部从晶体管M1的栅极流入,从晶体管M1的漏极流出时分为两路,一路经过电容C6再流入晶体管M2,再最终从晶体管M2的漏极流出,另外一路高频信号经过电感L4和电容C7到地。

2 仿真结果分析

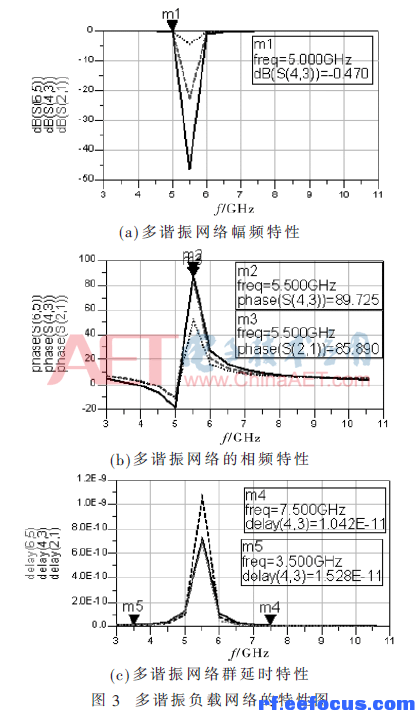

基于ADS仿真平台,将多谐振网络搭载到ADS软件下,调用S参数仿真器,在超宽频段内对幅频、相频以及网络特性上作出仿真,结果如图3所示。点线代表图1(a)提出的电路结构,长虚线表示图1(b)电路结构,长实线表示图1(c)电路结构。图3(a)展示出本文提出的多谐振网络的优势,干扰信号的衰减性强,上下边频拥有非常平坦的导通特性。图3(b)展示了多谐振网络的相位特性,本文提出的结构在WLAN信号的中心频率点5.5 GHz处的相频特性相差达到了89.725°,较之图1(a)和图1(b)多谐振网络能更好地使来自WLAN的干扰信号发生正交化,干扰信号就很容易被后续的相位鉴频器检查出来,从而更好地实现相频上的选择特性。图3(c)表现了多谐振网络的群延时特性,上下边频群延时都保持在同一数量级上,而在WLAN频带里则产生高量级的延迟,体现了频带选择网络对载波包络良好的选择性。

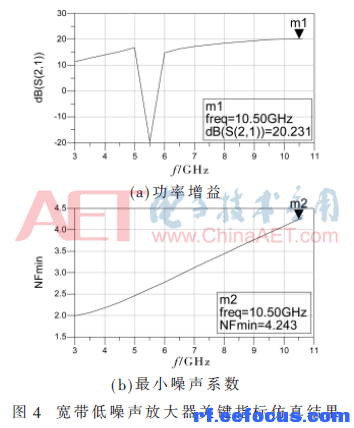

基于0.18 μm CMOS工艺利用ADS仿真软件对整个频带选择性的低噪声放大电路进行仿真,其结果如图4所示。其图4(a)显示了放大器的放大性能,也很好地反映出多谐振网络对无用信号的选频能力。上下通频带内,放大电路的增益超过10 dB,并对无用信号的幅度衰减也达到-20 dB。图4(b)为电路最小噪声系数随频率的变化关系,可以看出电路噪声性能良好,最小噪声系数小于4.25 dB。

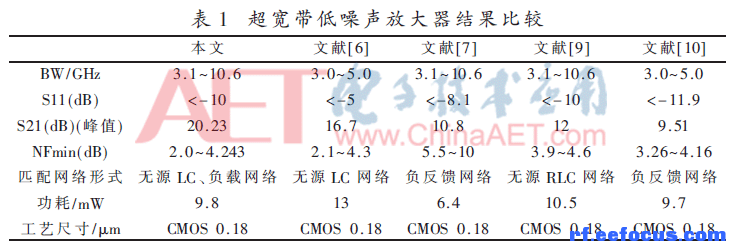

由表1中的参考数据可以说明:由于采用了无源LC输入匹配网络和电流复用结构,本电路的结构与参考文献相比较在其他性能参数略有缺憾的条件下具有工作带宽大、增益大、噪声较低、功耗较低的优点。

3 结论

本文论述了一种具有频带选择性的超宽带低噪声放大器的设计,提出新的多谐振负载选频网络以及引入电感源极负反馈的放大电路结构,最终使得放大电路在噪声和功率传输下都获得了良好的性能。仿真结果表明:在3.1 GHz~10.6 GHz频带内,稳定性良好,S11小于-10 dB,最大功率传输增益为20.23 dB,最小噪声系数在4.25 dB以下。同时与其他文献结果比较,该结构具有工作带宽大、功耗较低、面积省、增益大等优点,具有应用价值。

参考文献

[1] PARK B,LEE K,CHOI S,et al.A 3.1-10.6 GHz RF receiver front-end in 0.18 μm CMOS for ultra-wideband applications[J].IEEE MTT-S International Microwave Symposium digest.IEEE MTT-S International Microwave Symposium,2010:1616-1619.

[2] MIYAKE H,KITAZAWA S,ISHIZAKI T,et al.A miniaturized monolithic dual band filter using ceramic lamination technique for dual mode portable telephones[J].Journal of Bacteriology,1997,2(3):1333-44.

[3] PARK B H,JUNG J H.Design of a full-band CMOS UWB receiver and fast-hopping carrier generator for 3.1-10.6 GHz[J].Analog Integrated Circuits & Signal Processing,2014,79(1):45-56.

[4] PERUMANA B G,ZHAN J H C,TAYLOR S S,et al.Resistive-Feedback CMOS low-noise amplifiers for multiband applications[J].IEEE Transactions on Microwave Theory & Techniques,2008,56(5):1218-1225.

[5] CUSMAI G,BRANDOLINI M,ROSSI P,et al.A 0.18 μm CMOS selective receiver front-end for UWB applications[J].IEEE Journal of Solid-State Circuits,2006,41(8):1764-1771.

[6] ALAVI-RAD H,ZIABAKHSH S,ZIABAKHSH S,et al.A 0.9 V CMOS 3-5 GHz broadband flat gain low-noise amplifier for ultra-wide band receivers[J].Electrical & Computer Engineering Canadian Journal of,2013,36(2):87-91.

[7] HSU M T,HSIEH Y C,OU A C.Design of low power UWB CMOS LNA using RC feedback and body-bias technology[C].ASIC(ASICON),2013 IEEE 10th International Conference on.IEEE,2013:1-4.

[8] 赵常余.具有频带选择性的超宽带低噪声放大器的设计[D].绵阳:西南科技大学,2010.

[9] 华明清,王志功,李智群.0.18 μm CMOS 3.1~10.6 GHz超宽带低噪声放大器设计[J].电路与系统学报,2007,12(1):44-47.

[10] 王巍,彭能,王颖,等.3~5 GHz超宽带并联负反馈低噪声放大器的设计[J].微电子学,2011,41(1):10-14.

随着无线通信技术的发展和广泛应用,频率的需求越来越高,带宽也越来越宽,使得传统的窄带系统已经无法满足大流量数据传输的需求,因此宽带无线通信电路设计成为研究热点。2002年2月14日,美国联邦通信委员会(FCC)正式立法开放3.1~10.6 GHz频段给UWB系统作免执照使用。UWB技术具有发射功率较低、占空比低和抗干扰等特点,被应用在无线电话会议、无线短距离数据传送等诸多领域[1-2]。然而在FCC开放的频谱中来自授权频带WLAN的信号对免执照使用的频段UWB存在很强的干扰。UWB信号是微弱信号(频谱密度为-41.3 dBm/MHz),可比拟噪声甚至比一些噪声的频谱密度更低,所以UWB信号不会对WLAN信号产生明显的影响[3]。考虑到这两种无线局域网的使用区域出现交叠,致使UWB信号在5~6 GHz频段内完全被WLAN信号所淹没的情况,许多文献都进行了深入的研究。文献[2]设计了一个带阻滤波器来滤除WLAN信号,然而这种方法不仅要求整个通频带平坦度要好,滤波器在截止频率处的衰减响应更加陡峭,而且滤波后产生极大损耗和相移。同样使用多个LNA累叠的方式[4],来放大各自频段的UWB信号,这种方法不但增加了设计的工作量而且增加了成本。文献[5]则是设计了多谐振负载网络来实现整个频带的选择性,在整个系统中实现了对WLAN信号的屏蔽。

对此,本文也采用这种实时放大与选择的工作方式,对多谐振负载网络进行更深入的研究与设计,提出更加优良的多谐振负载网络,实现优于各文献的频带选择性。鉴于此,设计一种具有频带自主选择性的超宽带放大器[6-7],使之既能屏蔽来自授权频带信号的干扰,又能同时放大UWB下边带(3.1~5 GHz)及上边带(6~10.6 GHz)的信号,成为本文研究的重点,而能实现这种频带选择性的多谐振负载网络的设计更是本文工作的重要核心。

1 电路设计

整个电路的设计主要包括具有频带选择性的多谐振负载网络设计和放大器结构设计两个部分。

1.1 具有频带选择性的多谐振负载网络

本文通过对谐振特性的研究,设计了一种全新的具有频带选择性的多谐振负载网络结构,如图2所示,它能更好地屏蔽来自授权频带信号的干扰,又能通过UWB下边带和上边带信号。

图1(a)、图1(b)和图1(c)分别展示了3种多谐振网络结构,这3种网络均可实现频带选择性。其中图1(a)是文献[5]提出的结构,两电容和两电感简洁而有效地实现了宽频带上的选择特性;图1(b)是文献[8]提出的双串联双并联结构,引入调谐电容C2作为网络优化元件,降低了多谐振网络对高电感值的依赖,提升了多谐振网络频带选择性能。图1(c)是本文所提出的结构,引入调谐电容C1的双串联双并联结构,不仅提升了频带选择性能,而且更加强了对WLAN信号的屏蔽作用。

当频率从低到高时,受到电感扼流作用的影响,阻抗值是不断增加的。根据多谐振网络的拓扑结构,多谐振负载网络总的阻抗为:

从式(1)可以看出,多谐振负载阻抗的分子项由角频率的偶次项组成,分母由奇次谐波分量构成。由于工作在吉赫兹频段,为了能对信号产生调谐作用,电感和电容的量级确定为纳亨级和皮法级。由此可知:

由于谐波分量次数越高其值越小,所以Ztotal的分子值大于分母值,当且仅当f=5.5 GHz即为有约束条件的极值点:

当频率为5 GHz和6 GHz处,阻抗值为10logZtotal=0 dB的间断点,此时开始出现衰减特征。由此可知:

假设当C2=C3时,可得Ztotal,5 GHz=Ztotal,6 GHz。工作在最高频点10.6 GHz处,最大允许的负载网络的损耗为3 dB,即是:

可推导得C2<2/(2π×10.6×109)=30 pF。

通过仿真软件MATLAB进行编程仿真,C2初始值设定为30 pF。通过不断降低C2的值进行迭代运算,当C2=1.82 fF时,可得到本文提出的多谐振拓扑结构的最佳选择特性,这时L1=0.355 nH,L2=0.25 nH,C1=0.55 pF,C3=3.001 pF。

1.2 放大器结构设计

超宽带低噪声放大器是UWB无线接收机中的一个重要的模块,它必须在很宽的频带范围里提供足够高的增益和引入尽可能小的噪声,因此选择一个良好的电路拓扑结构来实现其性能要求是很重要的[9]。

电感源极负反馈结构其实采用的是共源极的放大电路,它是低噪声放大器很常用的一种电路[10]。本文采用电感源极负反馈的共源共栅结构,同时引入电流复用结构,构建出完整的频带选择性的超宽带放大电路,如图2所示。在M1源极引入一串联电感,此电感在较高品质因数下几乎不引入噪声。在工作频率内,加载在M1栅极的电感与MOS管的等效电路中的输入回路中的电容恰好形成谐振,可实现输入阻抗匹配。由于两个晶体管M1和M2在同一条偏置电路上,电流的功耗即为原来的一半,因为高频信号首先全部从晶体管M1的栅极流入,从晶体管M1的漏极流出时分为两路,一路经过电容C6再流入晶体管M2,再最终从晶体管M2的漏极流出,另外一路高频信号经过电感L4和电容C7到地。

2 仿真结果分析

基于ADS仿真平台,将多谐振网络搭载到ADS软件下,调用S参数仿真器,在超宽频段内对幅频、相频以及网络特性上作出仿真,结果如图3所示。点线代表图1(a)提出的电路结构,长虚线表示图1(b)电路结构,长实线表示图1(c)电路结构。图3(a)展示出本文提出的多谐振网络的优势,干扰信号的衰减性强,上下边频拥有非常平坦的导通特性。图3(b)展示了多谐振网络的相位特性,本文提出的结构在WLAN信号的中心频率点5.5 GHz处的相频特性相差达到了89.725°,较之图1(a)和图1(b)多谐振网络能更好地使来自WLAN的干扰信号发生正交化,干扰信号就很容易被后续的相位鉴频器检查出来,从而更好地实现相频上的选择特性。图3(c)表现了多谐振网络的群延时特性,上下边频群延时都保持在同一数量级上,而在WLAN频带里则产生高量级的延迟,体现了频带选择网络对载波包络良好的选择性。

基于0.18 μm CMOS工艺利用ADS仿真软件对整个频带选择性的低噪声放大电路进行仿真,其结果如图4所示。其图4(a)显示了放大器的放大性能,也很好地反映出多谐振网络对无用信号的选频能力。上下通频带内,放大电路的增益超过10 dB,并对无用信号的幅度衰减也达到-20 dB。图4(b)为电路最小噪声系数随频率的变化关系,可以看出电路噪声性能良好,最小噪声系数小于4.25 dB。

由表1中的参考数据可以说明:由于采用了无源LC输入匹配网络和电流复用结构,本电路的结构与参考文献相比较在其他性能参数略有缺憾的条件下具有工作带宽大、增益大、噪声较低、功耗较低的优点。

3 结论

本文论述了一种具有频带选择性的超宽带低噪声放大器的设计,提出新的多谐振负载选频网络以及引入电感源极负反馈的放大电路结构,最终使得放大电路在噪声和功率传输下都获得了良好的性能。仿真结果表明:在3.1 GHz~10.6 GHz频带内,稳定性良好,S11小于-10 dB,最大功率传输增益为20.23 dB,最小噪声系数在4.25 dB以下。同时与其他文献结果比较,该结构具有工作带宽大、功耗较低、面积省、增益大等优点,具有应用价值。

参考文献

[1] PARK B,LEE K,CHOI S,et al.A 3.1-10.6 GHz RF receiver front-end in 0.18 μm CMOS for ultra-wideband applications[J].IEEE MTT-S International Microwave Symposium digest.IEEE MTT-S International Microwave Symposium,2010:1616-1619.

[2] MIYAKE H,KITAZAWA S,ISHIZAKI T,et al.A miniaturized monolithic dual band filter using ceramic lamination technique for dual mode portable telephones[J].Journal of Bacteriology,1997,2(3):1333-44.

[3] PARK B H,JUNG J H.Design of a full-band CMOS UWB receiver and fast-hopping carrier generator for 3.1-10.6 GHz[J].Analog Integrated Circuits & Signal Processing,2014,79(1):45-56.

[4] PERUMANA B G,ZHAN J H C,TAYLOR S S,et al.Resistive-Feedback CMOS low-noise amplifiers for multiband applications[J].IEEE Transactions on Microwave Theory & Techniques,2008,56(5):1218-1225.

[5] CUSMAI G,BRANDOLINI M,ROSSI P,et al.A 0.18 μm CMOS selective receiver front-end for UWB applications[J].IEEE Journal of Solid-State Circuits,2006,41(8):1764-1771.

[6] ALAVI-RAD H,ZIABAKHSH S,ZIABAKHSH S,et al.A 0.9 V CMOS 3-5 GHz broadband flat gain low-noise amplifier for ultra-wide band receivers[J].Electrical & Computer Engineering Canadian Journal of,2013,36(2):87-91.

[7] HSU M T,HSIEH Y C,OU A C.Design of low power UWB CMOS LNA using RC feedback and body-bias technology[C].ASIC(ASICON),2013 IEEE 10th International Conference on.IEEE,2013:1-4.

[8] 赵常余.具有频带选择性的超宽带低噪声放大器的设计[D].绵阳:西南科技大学,2010.

[9] 华明清,王志功,李智群.0.18 μm CMOS 3.1~10.6 GHz超宽带低噪声放大器设计[J].电路与系统学报,2007,12(1):44-47.

[10] 王巍,彭能,王颖,等.3~5 GHz超宽带并联负反馈低噪声放大器的设计[J].微电子学,2011,41(1):10-14.