硬件设计新手入门之精读电路图 (三)

时间:10-02

整理:3721RD

点击:

上篇最后问到关于内存连接器CS有两个信号,而BS却有三个信号的问题。不知大家有没有搞清楚。这里设计到两个不同的概念:bank 和 rank。大家都知道内存条是由不同的内存颗粒(一个单独的内存芯片)组成的。每个内存颗粒内部又可分成不同的bank。现在的处理器都是64位的,而一颗内存颗粒往往只有4/8/16位,因而需要几颗颗粒组合在一起才能输出64位。这些组合在一起的实现64位输出的颗粒叫一个rank。BS信号用来选择一个颗粒内部的具体bank,而CS信号用来选择rank。理解了这些概念后就知道其实CS 和BS信号数量之间没有关系,完全由bank 和rank数量来决定。在 DDR2设计中,bank最多为8个,所以需要3根信号进行选择;而rank最多为4个,因而只要两根信号作为片选就可以了。

接着第二篇,我们接着分析X86平台的嵌入式设计的Atom(凌动)处理器的连接电路。

处理器DMI, 显示及时钟信号接口

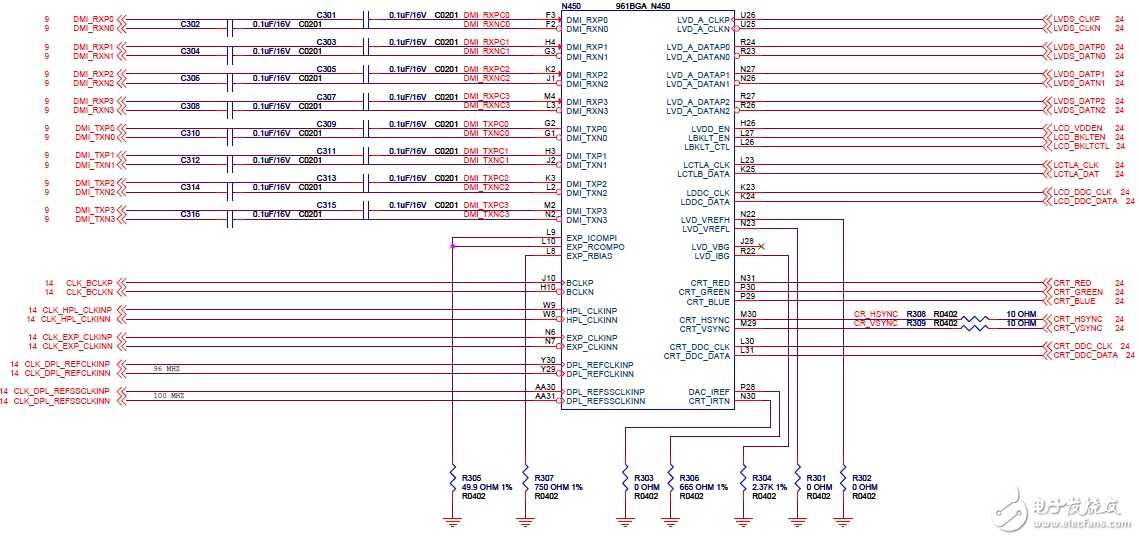

下图是该处理器相关接口信号的电路连接。这些信号的连接也不复杂,与对应得芯片以及连接器直接相连。具体分析如下:

- 电路左上部分是DMI信号连接,全称是Direct Media Interface。这是英特尔内部开发的用于南北桥之间连接的串行总线。在该设计中,由于北桥的功能已集成到处理器中,因此DMI直接连接该(凌动)处理器和ICH8南桥。该总线主要包含由南桥发到处理器的4组RX差分信号对,以及由处理器发到南桥的4组TX信号对。

- EXP_ICOMP/RCOMP是DMI总线的电流和阻抗补偿信号。根据芯片的设计guideline, 这两个信号连接在一起,工作50欧姆电阻连接到地。EXP_RBIAS是该总线的偏置设定控制,根据设计规范,通过750欧姆电阻连接到地。至于为什么要这样连接,这些电阻是如何选定的,就要的芯片内部的电路设计有相当的了解。通常情况,芯片公司不会透露相关细节,所以一般直接照着设计规范的要求连接就可以了。

- 时钟信号-由于处理器功能较多,因而需要较多的时钟信号,由核心逻辑电路用的时钟,DMI 接口总线用的时钟,显示接口所使用的时钟信号等等。这些时钟信号都由时钟发生器芯片产生。因此电路图左下部分时钟信号都连接到位于14页的时钟发生器芯片。

- 电路图的右边部分是显示接口信号的连接。右上部分是数字显示LVDS 接口,没什么特别好说的,相关信号连接到位于24页的对应引脚。LVD_VREFH/L,根据datasheet,这是两个预留的引脚定义,可以连到地,或者不连接。在本设计中,用0欧姆的电阻连到地,这样也预留了调试的空间。万一接地出现问题,可以很方便地把0欧姆电阻去掉,而不用更改PCB设计。

- 电路图的右下部分是模拟显示VGA接口信号,信号也是连接到位于24页的连接器。CRT_IRTN是用于连接电流回路通道,因而根据规范直接连接到地。本设计也是串接0欧姆电阻,以备将来调试需要。DCA_IREF,根据规范,通过665欧姆1%精度电阻连接到地。因此就按照规范要求相连接。由此也可以看出,很多引脚的连接一定要参照datasheet 和设计guideline的要求来做。

今天分享就到这里。同样问个问题:DMI总线的信号中串接一个0.1uf的电容,该电容有什么作用呢?欢迎一起学习讨论。

未完待续。新手入门,学习更多硬件设计知识和经验,请扫一扫或长按下面二维码,关注微信公众号:超硬工程师。

电路图加载有点问题,一直加不上。看原文可点连接:

http://mp.weixin.qq.com/s?__biz=MzI2NTA1Mjc3OA==&mid=400892254&idx=1&sn=5e0a098fe6c76b1ccb4b7c0fd3036e8a&scene=0#wechat_redirect

终于可以加电路图了

电路分析四正在写作中,希望继续关注

硬件电路分享学习系列第4篇已经发布了

硬件设计新手入门之精读电路图 (三)