四的疑惑

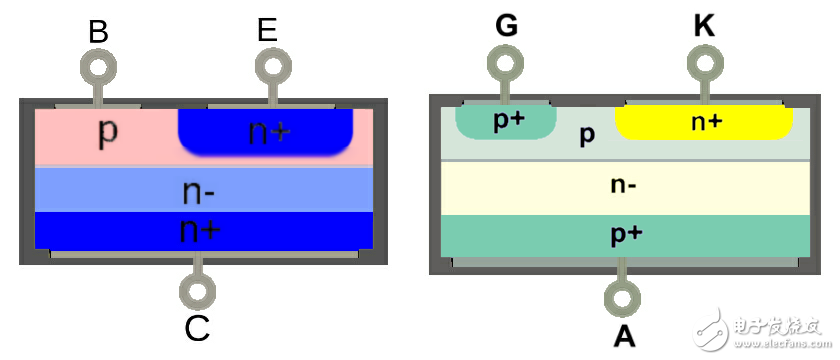

三极管是模拟型的有源器件,拿它做开关不是不行,你得要持续地施以足量的驱动才会持续地完全开通,跟一般的开关用三极管相比,四层晶体管在开关方面所需的各项性能指标的优化更深更全,而线性度则更形忽略。

晶体三极管的原理,是势垒的控制,BJT的功率流穿越结面,势垒无法完全消隐,FET的功率流从结旁经过,没有饱和压降,但因沟道电阻受制于芯材,通常比BJT要大,如果沟道能受到电导调制,阻力即可大减,此效果在一般三極管看来是无法做到的了,而PNPN架构则可以,也许这就是强功率有源器件都向四层化发展的原因吧。

集成电路的每一级都是完整的,而有源器件本身却是每增添一层就相当于加了一级,但其属性依然是有源器件一个而不是三端集成电路一枚!

为求令强功率开关元件的性能更进一步,打从IGBT以后的管子,其层数亦更进一步,不过,对这些高阶元件我不打算在此讨论,只是想以一个门外汉的所知所学,谈谈这个PNPN四层架构如何弄出不同的功能来。

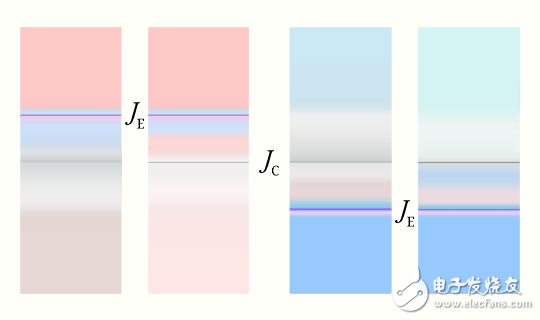

且先往BJT进内看看,BJT有两个结,结的厚度跟掺杂浓度合符反比规则,Jc基区段的厚度受Je的状态影响,但不为Vcc所左右,而Jc的集电区段只受Vcc影响,cascode拓扑的共射级被共基级钳位,情况就如测量h参数时设置的那个『交流短路』,在此状态下,Jc集电极段的厚度是不随Ic而变的。

基区虽薄,却是讯号的接收处及功率通道的咽喉,基区联同集电层组建出集电结,在BJT中,集电区是厚,大,淡的,但其实,淡才是必须的,厚和大也是应该的,但可控硅的集电区就是对方的基区,厚不了,

正由于基区对有源功能是如此的重要,故在可控硅中,层的名称只有基,没有集(对方的基区就是集电区),但集电结却永远是集电结,可控硅的通断就是取决于此结,这跟BJT没啥分别,

基集的共性,都是淡,所以,由两个基区构成的集电结可以耐受很高的电压,但正因构成集电结的是两个基区,即使採用异质射极,基区掺杂也不能像HBT那样比射极还浓,否则,耐压就会大减甚至喪失阻断能力,

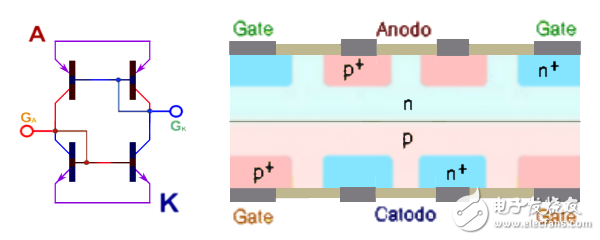

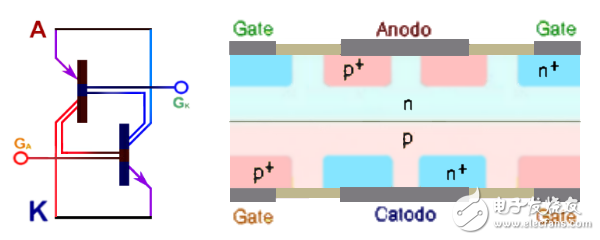

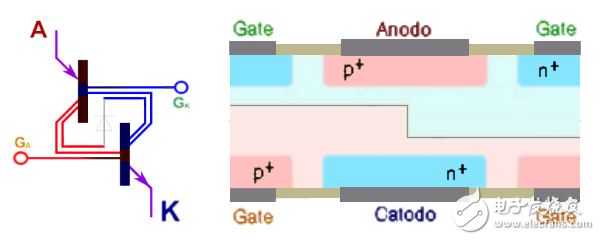

图中,从左到右,1显示可控硅的基本构造及各结在未馈电时的情况,2显示的是Ic与Ib(两个发射结的空乏处消失了),3则显示Ie(扩散与漂移),4嘛,可控硅开通时大概就是这样,两种载流子混着走,漫滩了,三个结都被淹没,只剩下0.6V的饱和压降(逃了和尚跑不了庙,那三条黄线代表的是可控硅的物理结面)。

跟三极管相比,可控硅才是货真价实的开关,但晶体管开关电路却不包括可控硅及其族类,

开与关,是两个稳态,自保持和可翻转,是双稳态的实现条件, 个人认为,真正的双稳,其翻转的策动方式应该一致,要么都靠触发,要么都在电源上做文章, 以此论之,可控硅就只能叫做准双稳,

对于可控硅的学习认知,绝大多数都是从互补管交连拓扑入手,如果你对BJT原理的了解较深,就会发觉BJT其实只是用了集电结的一半,

给NPN管基极接个上拉开关,管子不就可饱和导通了吗,反偏的PN结既然还可传导另一种载流子,那么,把NPN管的集极造薄并且在头上放个P,就等于接上了PNP管,Ib中的关键载流子就可由这个PNP给予,不需讯号也能维持导通,这就是可控硅的运作机制。

噢,问题来了,BJT的导通压降为零当然理想不过,至少也应该低于二极管的门槛电压才对头吧,那可好了,可控硅中的这个『PNP』只有基区,却没有基极,那么,它的「Ube」在哪,饱和时的「集电结」正偏是怎么样个偏法?

可控硅中的电流跟导线中的一样,都是直通通地涌过的,

可控硅是自持器件,两个「BJT」的增益愈高,正反馈就愈深重,愈是易通难断,至于资源分配,为求开得省力,小功率的应该是N管,而欲关得轻松,小功率的应该是P管,

跟BJT一样,可控硅也需要Ib,把可控硅开通,灌的是N管的Ib,触发开通时Ib是从闸极注入的,在基区里头挪动,开通后的『Ib』就是P管的整个Ic,从集电结哗啦啦的涌来,发射结从功率通道取得远超饱和所需的驱动,欲令可控硅关断,要抽掉的就是这P管的整个Ic!

闸极是N管的基极,载流量小,反向耐压低,对于这样的超量驱动而言,6给闸极反偏再大也只是杯水车薪,无济于事, 除非这些超量Ib可以直接一举抽掉,或闸极在深度饱和时对电流的减小有明显反应,而不是要减到小于维持电流时才有所动作,这器件才能够以触发方式关断,

假设,P与N的β都是10,那么,N管发射结吃的就是100Ib,想把可控硅关断,就必须令发射结剩下0.99……Ib才行,山洪海啸当前,神马抽水机下水道分洪区都是浮云了吧?!

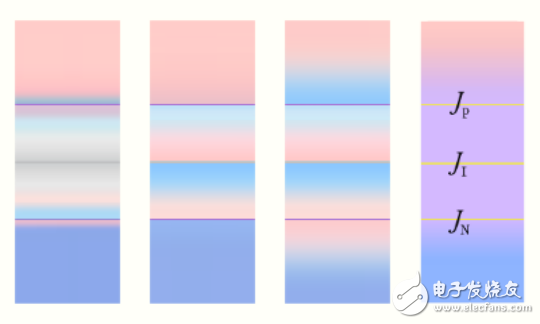

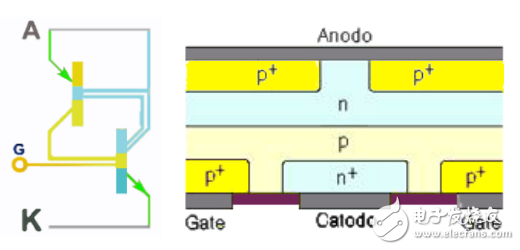

四层器件能否以触发关断,端赖布局,把射极造淡,基区做厚,可降低增益,从根本上减小自持能力,是使元件易较易关断的办法之一,另外就把两个「BJT」的耦合削弱,不让对方的『Ic』过多的进入发射结,

在真实结构中,每层都不能引入额外的阻抗,只能透过分流解决,把部份基区还原为集电极,就可把对方的发射结短路,起到了分流的作用,此法广为四层(及以上)的有源器件所採用,GTO及SCS等因而成为真正的双稳元件,而在强功率开关三极管中则可保证器件的模拟属性(线性指标似不考虑)及防止闩锁故障的发生,

注意,这短路並非把二极管的引脚短接,短路块是紧贴物理结面的,被短接的是结,不是极,结被短路,势垒就无法运作,这做法只会在发射结施行,基于有源器件本身的宽高比,基区总会有一定的横向电阻,

当发射结正偏,强大的功率电流贯通基区的接地部份时,横向电阻的效果就显露出来,在接近短路块的区域,这『横向电阻』正好作为假负载(势垒其实可有可无),把过剩的内部驱动分流掉(理论上,四层晶体管是模拟或双稳器件,可透过假负载的阻值来控制哩),而主要功能区因离短路块足够远,势垒受短路的影响小,有源器件的功能不会被破坏,

发射结短路法会降低『BJT』的视在β,因触发输入的Ib被分流了嘛,但由于对过剩流量的疏导,「关断增益」就得以提高,此法还有一个弊处,就是反偏不均甚至加不上,只能靠那「横向电阻」使『BJT』的耐压提高至BVcer,

GTO可以不在闸极(NPN部份)施行,IGBT是以场效应驱动的,更完全没这顾忌,以原理图论之,BJT跟MOSFET的结构可说是一样的,不同的只是控制方式,没有电气连系,就没有电导调制,功率通道就没有饱和压降但电阻就较同规格的BJT大了,

在IGBT中,受控部份的结构就像这模样,为避免闩锁故障的发生,设计者利用MOSFET跟BJT形成所需的条件差异,让这架构只剩下MOSFET功能,既然IGBT不需要NPN的Ib,故可在栅极使用发射结短路法,但对于PUT,SCS那些需要「Ib」的互补对称元件呢,那弊病可就逃不掉了。

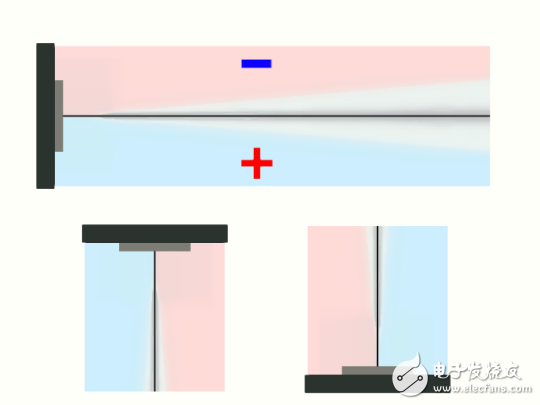

GTO的原理电路及实际结构

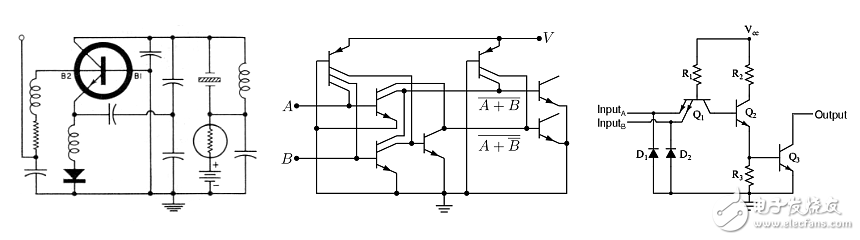

用互补BJT接成的仿可控硅电路,两个端子都是射极,遗憾的是,通过两个射极的都只是Ib,想引出Ic就要把负载连至集电极,

而在一切四层器件中,集极跟对方的射极直接组成发射结或共用端子,双方的Ic都能直通对方的射极或落到AK端子上,射极原本应有的载流能力不会被架空了,PNPN四层皆尽其用,

不过,事物往往无两全,双稳器件的关断确是个问题,可控硅关不断是因「Ib」过多,分流(发射结短路)可解决此问题,其实,第二射极的作用,就是使BJT转化成可控硅,但我发觉,其实並不需要把整个BJT都转化,只需改一点点就可以,那就变成等同于以小功率可控硅控制大功率BJT的拓扑,

Ic大流中本来就只有极小部份起着「Ib」的作用,设立分流机制后,『可控硅』承载的只是『BJT』的Ib,从BJT的Ib中取得保持导通状态所需的「Ib」,关断时需要抽掉的电流自然就小多了,而且,有源器件似乎有个规律,就是同一种元件,弱功率的总比强功率的快,而同样规格的可控硅比BJT慢得多(只有10%甚至更差),『可控硅』小了,整个元件的开关就可快点,闸极反偏问题虽没解决,但影响就小多了。

可控硅家族都是建基于BJT,但各自的具体结构却不一样,

根据它们的真实结构描绘其等效电路,你会发觉竟然就像TTL里头的多极BJT。