单片机双机并行通信中所遇到的问题及解决方法

时间:10-02

整理:3721RD

点击:

1 引言 本系统主要应用于双CPU电脑刺绣机中。为了减轻下位机的控制负担,更好的完成花样的刺绣。其次为下一步脱机工作做准备(即在机器刺绣的同时,为刺绣下一个花样做准备工作),这样一来,可以进一步提高工作效率。由于系统在最初研发中遭遇程序跑飞问题的困扰,于是提出了采用CPLD(可编程逻辑器件)的方式,以解决通讯干扰问题。 本系统采用的CPLD为 ATMEL公司生产的ATF1540AS器件,该器件是一种高性能、高密度复合可编程逻辑器件,简称CPLD,它利用ATMEL 的电可擦除存储器技术,有 64个逻辑宏单元和68个I/O端口,很容易和多个TTL、SSI、MSI、LSI和经典的PLDS组合使用。每个宏单元包括积项和积项多路选择器、 OR/XOR/CASCADE逻辑、触发器、输出选择和使能、输入逻辑阵列五个部分。ATF1504AS的增强选路开关增加了可用的门计数,提高了管脚锁存设计修改的成功率。 2 系统结构 系统的CPU采用W77E58,由ATF1504AS构成通信接口,系统框图如图1所示。 2.1 问题提出 电脑刺绣机为达到良好的人机界面交互功能,采用上下位机方式,下位机主要进行绣花动作的控制,上位机主要进行花样的跟踪。为了实现绣花的同时在液晶屏上进行绣花跟踪,单CPU方式存在系统资源透支, CPU处理数据将十分困难,于是提出了采用双CPU的工作方式,但同时带来一个问题—双CPU的通信问题。 2.2 解决方案 (1) 采用串行通信方式 优点:在由单片机组成的多机方式中,串行接口方式是最常用的。串行通信方式接口电路简单,可以方便实现长距离传输。抗干扰能力比较好。 缺点:传输数据慢,不适合实时数据传输。在数据传输要求高的情况下,容易造成瓶颈堵塞现象。 (2) 采用并行通信方式 优点:并行通信传输数据快,适合进行实时控制。 缺点:抗干扰能力差,不适合长距离传输,最大距离不超过5m。 由于本系统对数据传输的实时性要求比较高,并且上下位机之间的距离不超过3m,进行适当的抗干扰措施,完全可以达到系统的要求,所以确定采用并行通信方式。 2.3 具体措施 (1) 采用ATF1504AS(可编程逻辑器件)进行并行通信,减少分立器件所产生的杂散电容而带来的噪声干扰。 (2) 在输入数据端加斯密特电路(74LS14),将外部传输线上耦合噪声滤除掉。从而提高总线接收的抗干扰性能。 (3) 采用三态门驱动方式可以提高总线的抗干扰能力,因为三态门有三种状态输出,既所谓的低阻高电平、低阻低电平、高阻态(禁态)。由于三态门的输入具有的三态性,所以使三态门的信号源的负担减轻。有利于提高速度和抗干扰能力。 3 双CPU通信原理设计 3.1 双CPU通信原理图 从图2双CPU通信原理图中可以看出,在输入接口上都接上74LS14斯密特电路和74LS244三态门驱动器,以提高抗干扰能力。在SRZB、SCYX(上位机)及SRZB、SCYX(下位机)的握手信号线上接入74LS14斯密特电路,以提高抗干扰能力。

3.2 ATF1504AS内部原理图 由于篇幅有限,仅列出上位机的ATF1504AS的内部原理图如图3,下位机的ATF1504AS的内部原理图与此相类似。

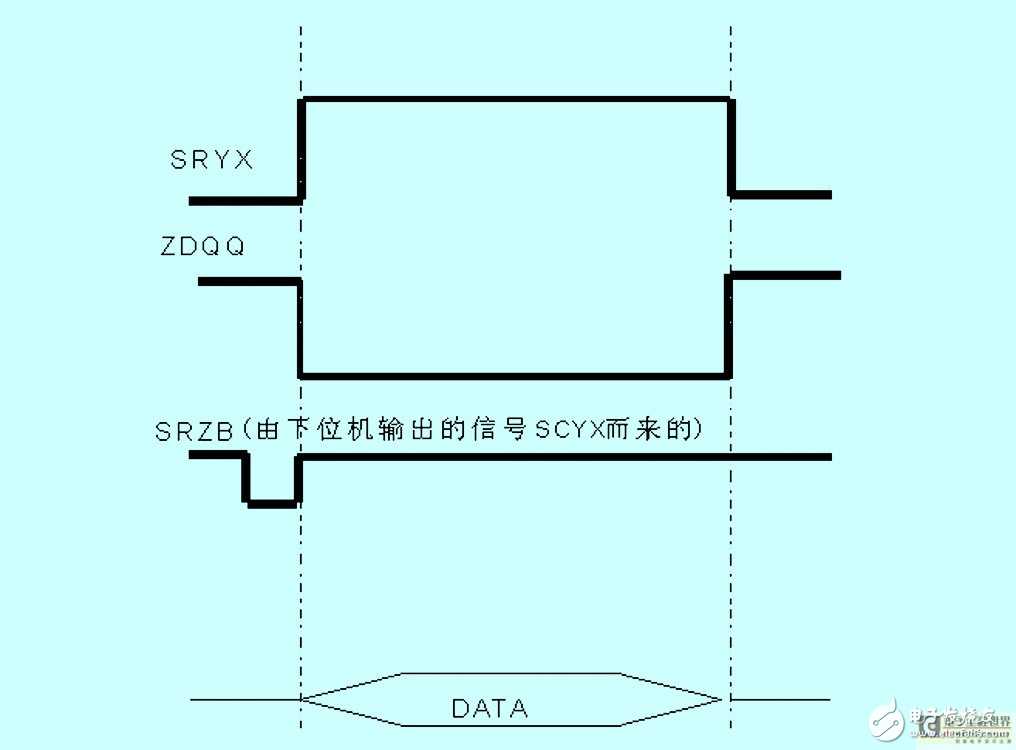

4 系统工作原理 4.1 上位机输入数据 如图3所示。在输入数据以前,通过对U1(74173)给U2(D触发器)进行初始化,即对U2的CLRN端输入一上升沿的脉冲,使U2清零。此时上位机 SRYX端为低电平,ZDQQ端为高电平。此时为接收数据做好准备。当下位机接收到上位机的SRYX端输出的低电平时,就可以发送数据到锁存器中,紧接着给上位机的SRZB端输出一个上升沿脉冲,U2的Q端(SRYX端)输出正脉冲,ZDQQ端经过反相器输出负脉冲。上位机在检测到ZDQQ端为低电平时,将数据线上的数据取出。紧接着通过对UI给U2进行进行初始化,完成对一个字节的读取,并为读取下一个字节做好准备。上位机输入数据信号波形图如图5所示。

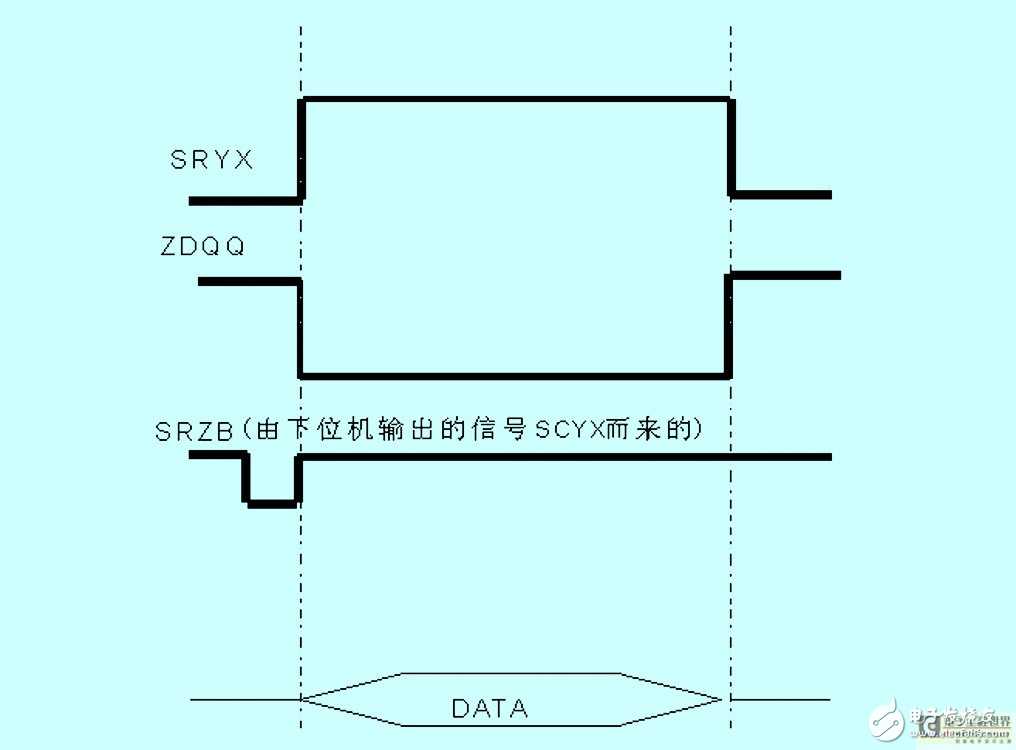

4.2 上位机输出数据 如图3所示在输出数据以前,通过对U1 (74173)给U3(D触发器)进行初始化,即对U3的PRN端输入一上升沿的脉冲,使U3输出置1。此时上位机的SCZB端经反相器输出低电平,U3 的Q端为高电平。此时为发送数据做好准备。当上位机的SCYX端接收输入的上升沿脉冲时,U3的Q端为低电平,当CPU检测到Q端为低电平时,就可以发送数据到锁存器中,紧接着通过上位机的SCZB端向下位机SRZB端输出一个上升沿脉冲。表示已发送数据,接着通过对U1给U2进行进行初始化。完成对一个字节的输出,并为输出下一个字节做好准备,上位机输出数据信号波形图如图4所示。

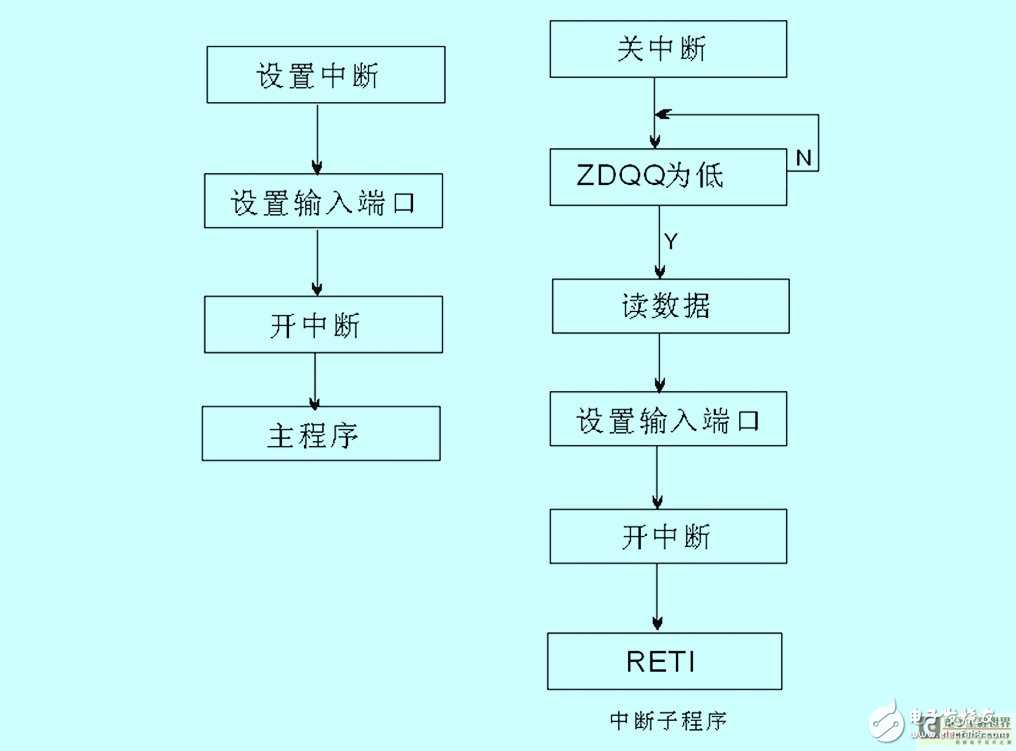

5 软件设计 5.1 程序流程设计 图6示出输入数据流程图,图7示出输出数据流程图。

5.2 部分程序清单 (1) 输入数据程序清单 ORG 0000H JMP START ORG 0003H JMP RESEVE START: MOV TCON,#0 ;设置中断INT0 MOV TMOD,#11H CALL SZSRDK ;设置输入端口 MOV IE,#81H MOV IP,#1 ;开中断 .. .. .. RESEVE: CLR EA ;开中断 PUSH PSW PUSH DPH PUSH DPL RESEV1: JB ZDQQ,RESEV1 ;判ZDQQ是否为低 MOV DPTR,#ADDR0 ;为U5(输入数据端口)的地址 MOVX A, @DPTR .. .. CALL SZSRDK POP DPL POP DPH POP PSW SETB EA RETI SZSRDK: CLRN EQU 2CH.0 CLR CLRN ; MOV DPTR,#ADDR1 ;为U1的地址 MOV A,2CH MOVX @DPTR,A SETB CLRN MOV A,2CH MOV DPTR,#ADDR1 MOVX @DPTR,A RET (2) 输出数据程序清单 SEND: MOV DPTR,#ADDR3 MOVX A,@DPTR JB ACC.0,SEND ;为U3的Q端输出 MOV DPTR,#ADDR4 ;为U4(输出端口)的地址 MOVX @DPTR,A CALL SZSCDK RET SZSCDK: PRN EQU 2CH.1 SETB PRN MOV DPTR,#ADDR1 ;为U1的地址 MOV A,2CH MOVX @DPTR,A CLR PRN MOV DPTR,#ADDR1 MOV A,2CH MOVX @DPTR,A RET

6 结束语 设计中采用了AT1504AS器件,该器件实现了硬件设计软件化,方便了硬件设计,缩短了设计周期,降低了设计成本,应用也十分方便,该系统经过采取以上措施后,以达到最初的设计要求。现产品已投放市场,市场的反映良好。

3.2 ATF1504AS内部原理图 由于篇幅有限,仅列出上位机的ATF1504AS的内部原理图如图3,下位机的ATF1504AS的内部原理图与此相类似。

4 系统工作原理 4.1 上位机输入数据 如图3所示。在输入数据以前,通过对U1(74173)给U2(D触发器)进行初始化,即对U2的CLRN端输入一上升沿的脉冲,使U2清零。此时上位机 SRYX端为低电平,ZDQQ端为高电平。此时为接收数据做好准备。当下位机接收到上位机的SRYX端输出的低电平时,就可以发送数据到锁存器中,紧接着给上位机的SRZB端输出一个上升沿脉冲,U2的Q端(SRYX端)输出正脉冲,ZDQQ端经过反相器输出负脉冲。上位机在检测到ZDQQ端为低电平时,将数据线上的数据取出。紧接着通过对UI给U2进行进行初始化,完成对一个字节的读取,并为读取下一个字节做好准备。上位机输入数据信号波形图如图5所示。

4.2 上位机输出数据 如图3所示在输出数据以前,通过对U1 (74173)给U3(D触发器)进行初始化,即对U3的PRN端输入一上升沿的脉冲,使U3输出置1。此时上位机的SCZB端经反相器输出低电平,U3 的Q端为高电平。此时为发送数据做好准备。当上位机的SCYX端接收输入的上升沿脉冲时,U3的Q端为低电平,当CPU检测到Q端为低电平时,就可以发送数据到锁存器中,紧接着通过上位机的SCZB端向下位机SRZB端输出一个上升沿脉冲。表示已发送数据,接着通过对U1给U2进行进行初始化。完成对一个字节的输出,并为输出下一个字节做好准备,上位机输出数据信号波形图如图4所示。

5 软件设计 5.1 程序流程设计 图6示出输入数据流程图,图7示出输出数据流程图。

5.2 部分程序清单 (1) 输入数据程序清单 ORG 0000H JMP START ORG 0003H JMP RESEVE START: MOV TCON,#0 ;设置中断INT0 MOV TMOD,#11H CALL SZSRDK ;设置输入端口 MOV IE,#81H MOV IP,#1 ;开中断 .. .. .. RESEVE: CLR EA ;开中断 PUSH PSW PUSH DPH PUSH DPL RESEV1: JB ZDQQ,RESEV1 ;判ZDQQ是否为低 MOV DPTR,#ADDR0 ;为U5(输入数据端口)的地址 MOVX A, @DPTR .. .. CALL SZSRDK POP DPL POP DPH POP PSW SETB EA RETI SZSRDK: CLRN EQU 2CH.0 CLR CLRN ; MOV DPTR,#ADDR1 ;为U1的地址 MOV A,2CH MOVX @DPTR,A SETB CLRN MOV A,2CH MOV DPTR,#ADDR1 MOVX @DPTR,A RET (2) 输出数据程序清单 SEND: MOV DPTR,#ADDR3 MOVX A,@DPTR JB ACC.0,SEND ;为U3的Q端输出 MOV DPTR,#ADDR4 ;为U4(输出端口)的地址 MOVX @DPTR,A CALL SZSCDK RET SZSCDK: PRN EQU 2CH.1 SETB PRN MOV DPTR,#ADDR1 ;为U1的地址 MOV A,2CH MOVX @DPTR,A CLR PRN MOV DPTR,#ADDR1 MOV A,2CH MOVX @DPTR,A RET

6 结束语 设计中采用了AT1504AS器件,该器件实现了硬件设计软件化,方便了硬件设计,缩短了设计周期,降低了设计成本,应用也十分方便,该系统经过采取以上措施后,以达到最初的设计要求。现产品已投放市场,市场的反映良好。

图四

图七

图六

图五

图一

图二

图三