sigrity自带ddr仿真报告的疑问

时间:10-02

整理:3721RD

点击:

使用的是自带的demo文件,跑的数率1.066g

在查看生成的报告时候发现有些地方跟实际手动测量不太吻合,不太清楚可能是那种缘故,现附图如下

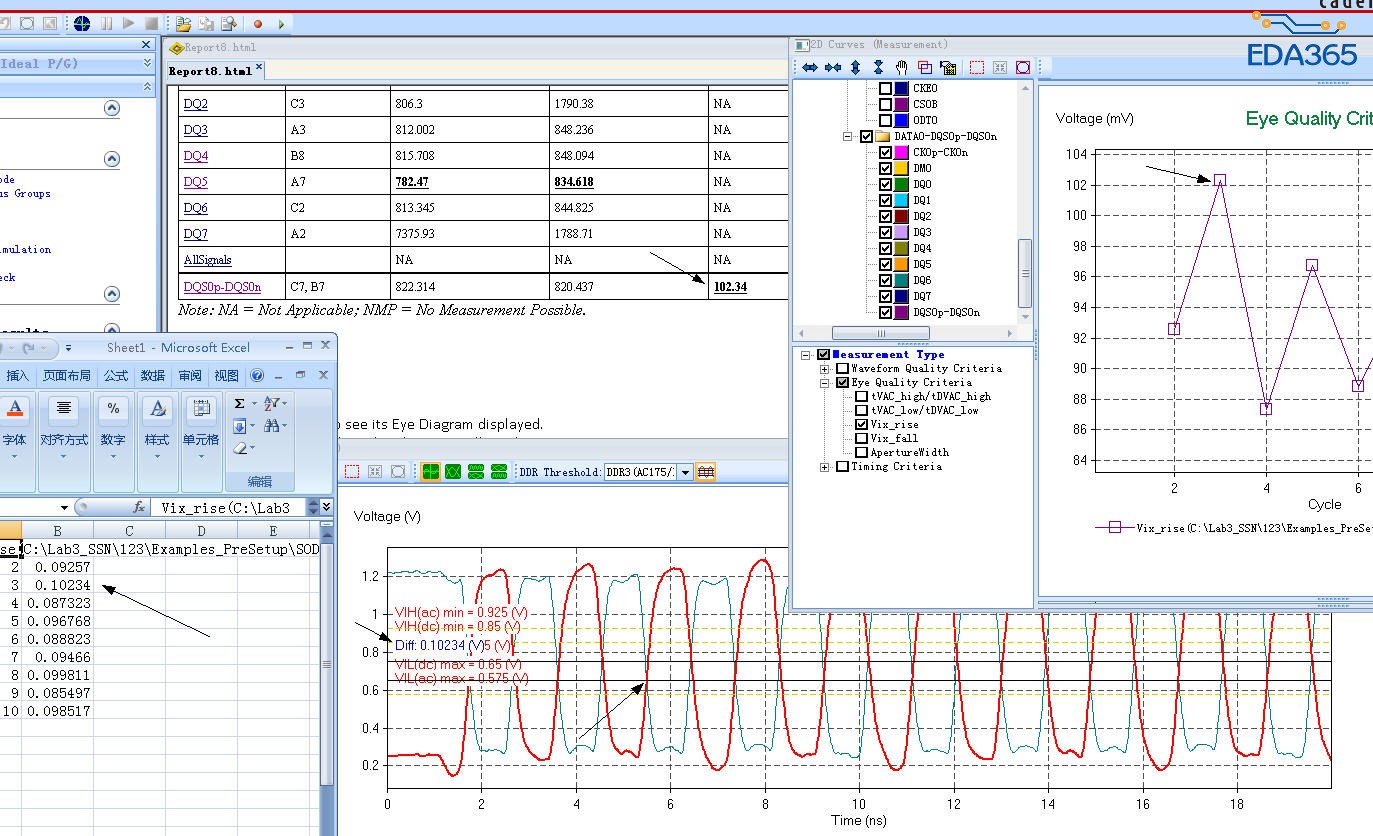

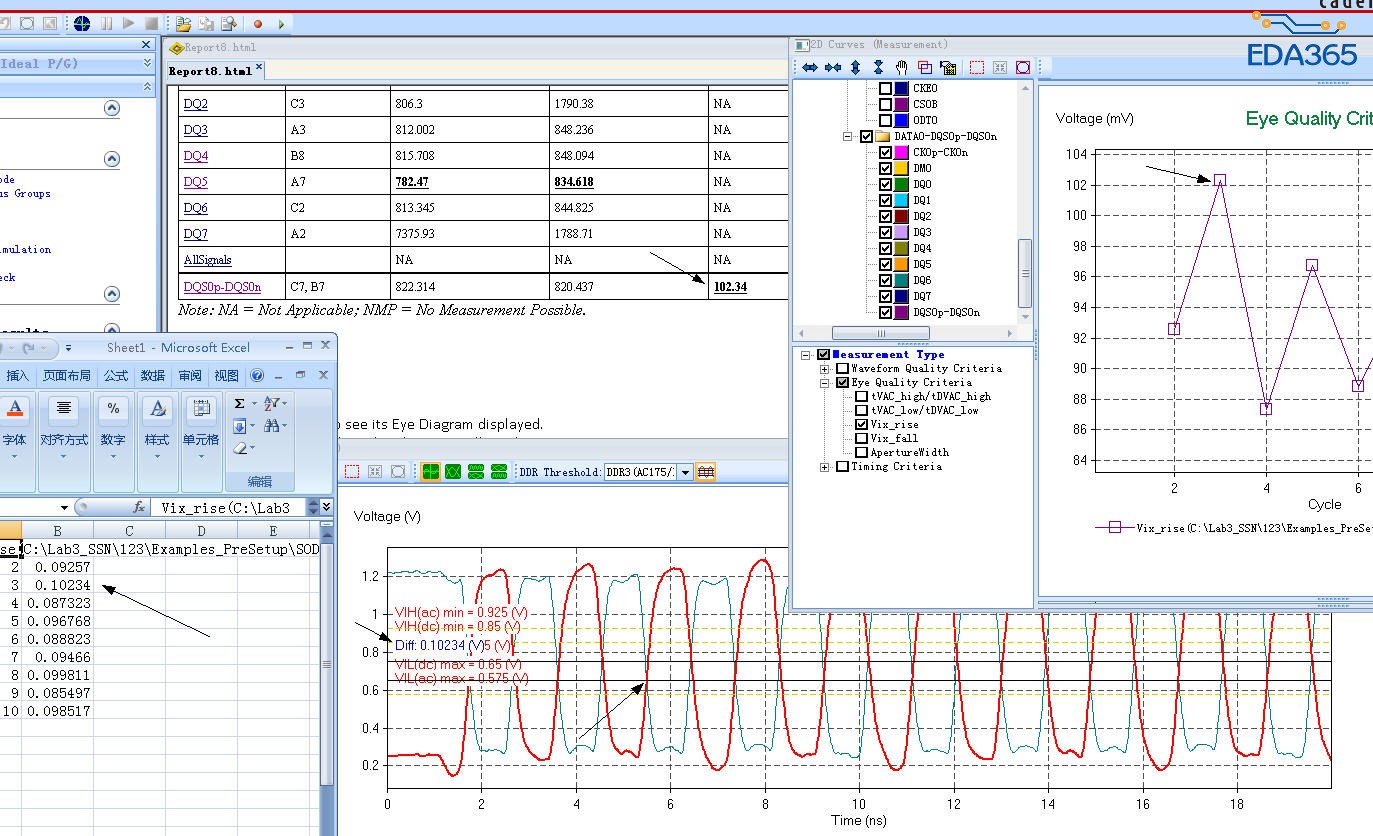

这是dqs的vix测试结果与手动测量对比,从上面看 应该是吻合的

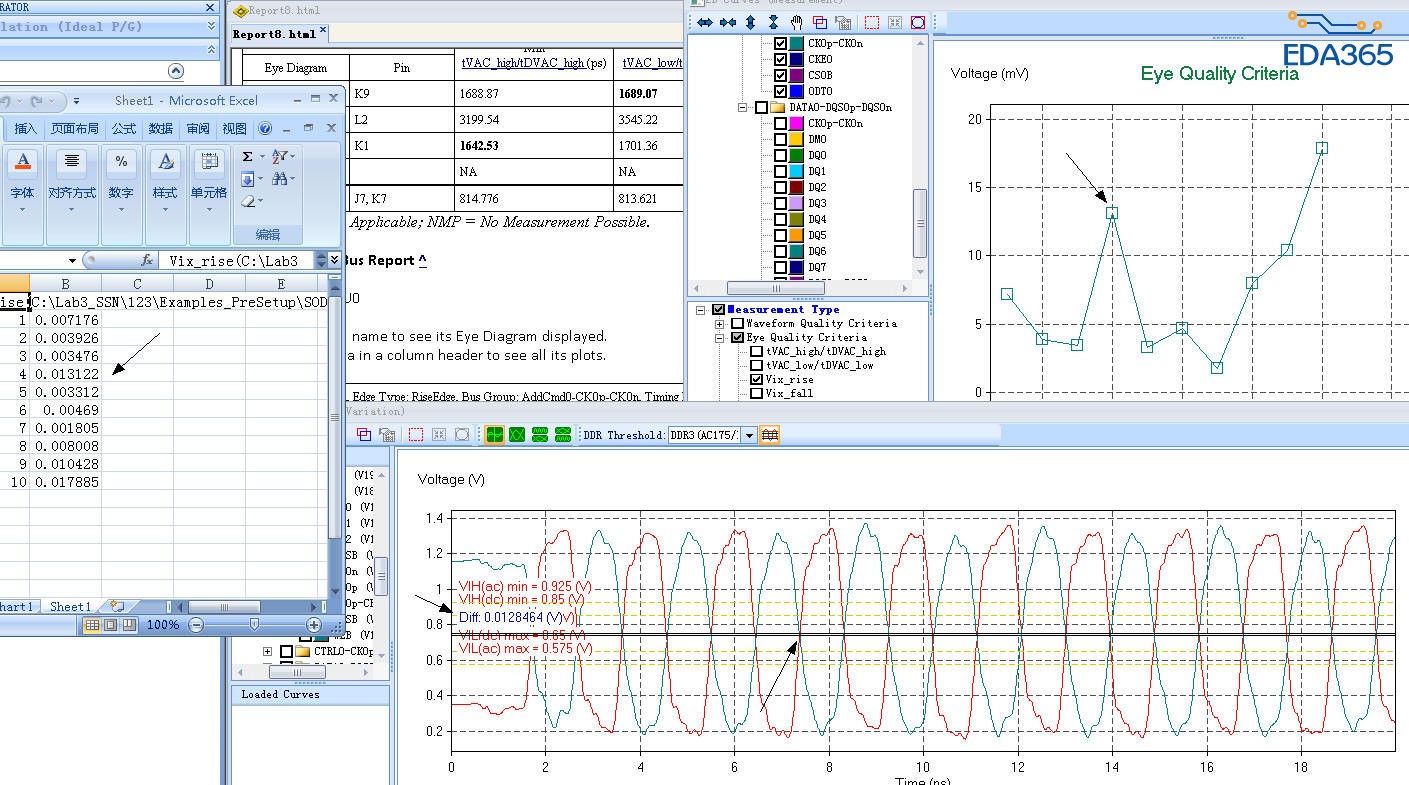

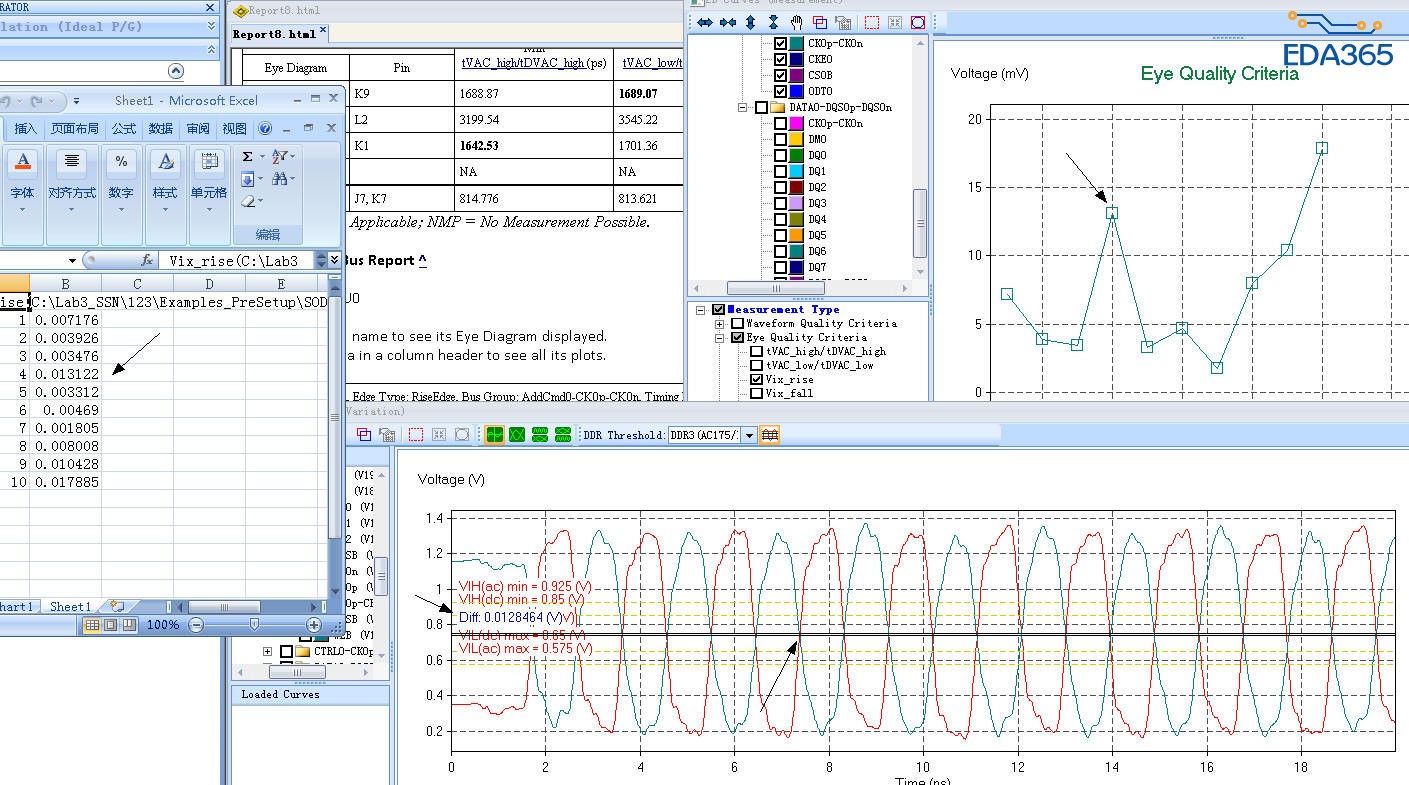

这是clk的vix测量结果与手动测量的对比,发现在数值上没有吻合?何故?

以dq0为例,报告是按ac175dc100进行生成的

从测量结果看dqs与dq的斜率都比规格里面的要大,在选择的时候依然按规格里面标注的最大来计算没?还是预测的?

因为按照规格里面的值计算的话,tds余量值跟测试报告里面的不一样

416.711-88-25 不等于182.25! 这个差别何故导致?

哪位朋友熟悉?

像报告里面显示的OOR与NMP为何没有测量到?这些需要如何才能正常显示出来?

在查看生成的报告时候发现有些地方跟实际手动测量不太吻合,不太清楚可能是那种缘故,现附图如下

这是dqs的vix测试结果与手动测量对比,从上面看 应该是吻合的

这是clk的vix测量结果与手动测量的对比,发现在数值上没有吻合?何故?

以dq0为例,报告是按ac175dc100进行生成的

从测量结果看dqs与dq的斜率都比规格里面的要大,在选择的时候依然按规格里面标注的最大来计算没?还是预测的?

因为按照规格里面的值计算的话,tds余量值跟测试报告里面的不一样

416.711-88-25 不等于182.25! 这个差别何故导致?

哪位朋友熟悉?

像报告里面显示的OOR与NMP为何没有测量到?这些需要如何才能正常显示出来?