System SI进行DDR仿真的问题

时间:10-02

整理:3721RD

点击:

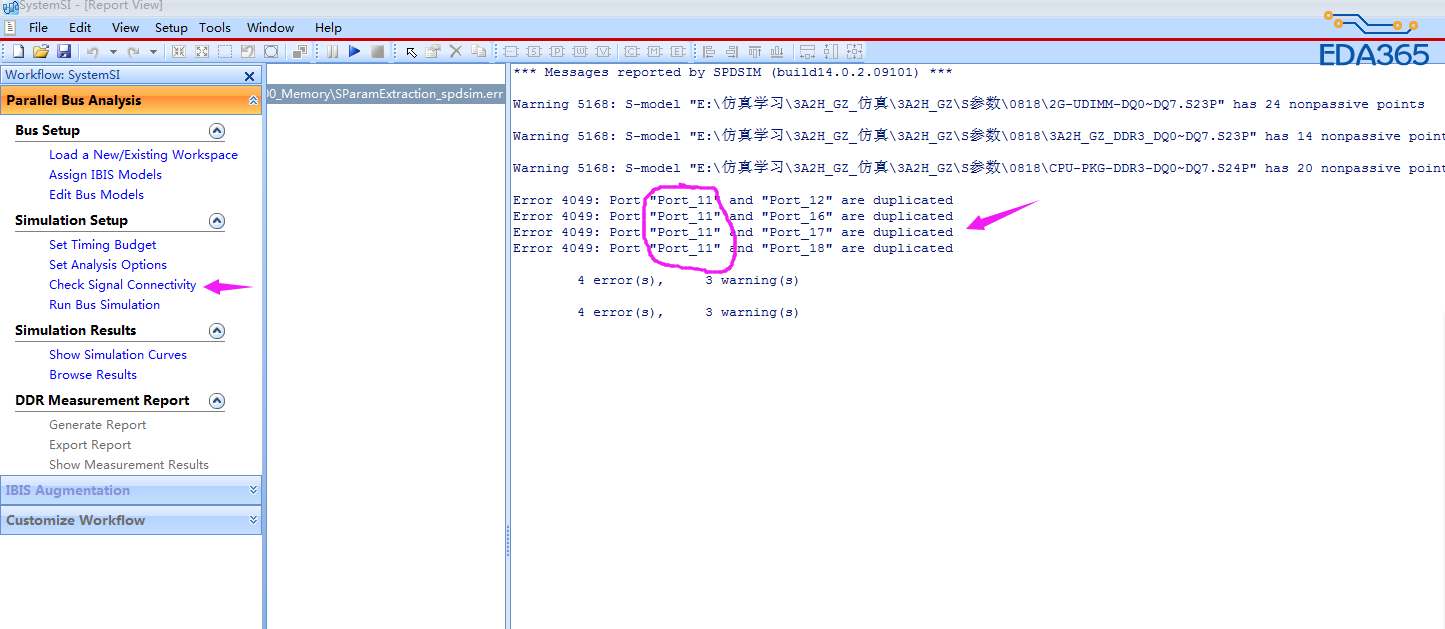

我在用system SI进行DDR仿真的时候,ibs模型已经S参数都已经加载后,在 check signal connectivity一步,点击后,报错。见附件。

请教各位大神,是哪里出了问题? 另外,port11,port12,16 名称是如何定义的?我都不知道问题往哪里定位。

救命啊,搞了好几天了。快崩溃了。

请教各位大神,是哪里出了问题? 另外,port11,port12,16 名称是如何定义的?我都不知道问题往哪里定位。

救命啊,搞了好几天了。快崩溃了。

首先,仿真路径最好不要有中文,因为有些软件会出错;其次,你的port定义有问题,检查一下你的port

解决方法很简单,11,12,16,17,18这5个port你一定是设置了一模一样的正馈和负馈。删掉4个或者按照自己的需要修改下正馈或负馈就可以了。

谢谢大神,我搞了好几天,终于找到问题在哪里了。添加VRM端口的时候,跟VDD_1.5V设置成了同样的正反馈。由于提取的S参数,只看S11,波形是正常的。就忽略了。 非常感谢大神指点!

谢谢大神,我搞了好几天,终于找到问题在哪里了。添加VRM端口的时候,跟VDD_1.5V设置成了同样的正反馈。由于提取的S参数,只看S11,波形是正常的。就忽略了。 非常感谢大神指点!