利用System SI进行DDR仿真,如何进行Pin Mapping?

时间:10-02

整理:3721RD

点击:

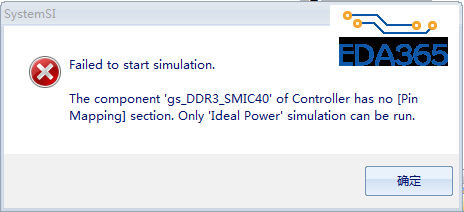

如标题,在用System SI进行DDR仿真的时候,给CPU附ibs模型后,软件会提示没有进行Pin Mapping。如果忽略的话,在进行仿真选项的时候,软件提示如果没有进行Pin Mapping,只能进行理想电仿真。

请教各位大神,如何进行Pin Mapping?有哪些原则或者要求?

请教各位大神,如何进行Pin Mapping?有哪些原则或者要求?

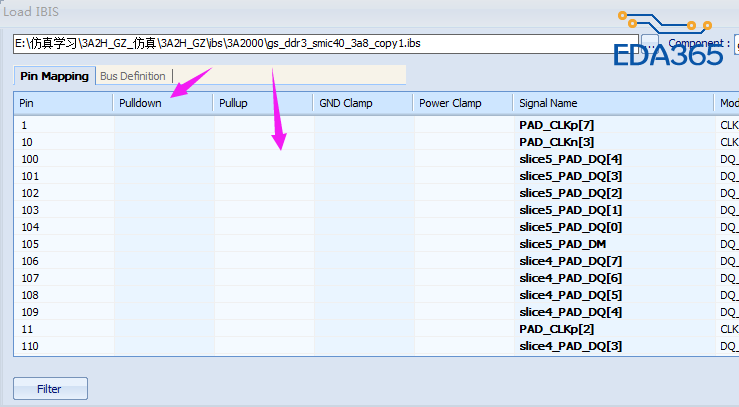

没有进行Pin Mapping

软件报错

将上拉/上钳位设置为POWER,将下拉/下钳位设置为GND,可选中多个pin同时修改

如有其它问题可贴出来

,多非常非常感谢大神指点!我先试试。

选中所有的pin,按照上面的方法进行统一设置,不需要加的软件不会加,所以不必担心加错;当然如果是EBD的就不要这么搞了,个别pin会出错