求教DDR时钟差分信号仿真

时间:10-02

整理:3721RD

点击:

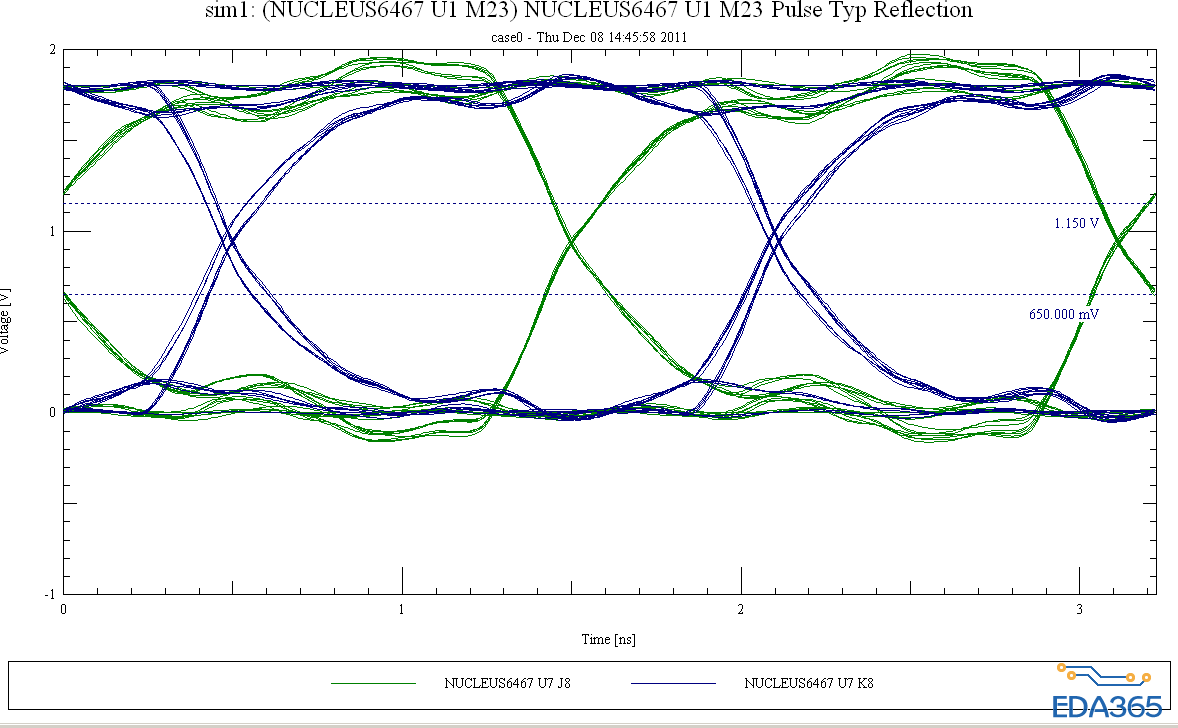

最近仿真DDR 时钟,仿真出来的波形和拓扑结构如下所示:

图1: 驱动端;图2、3:接受端

图4:驱动端发出时钟差分波形;

图5、6:接受端收到时钟差分波形。

仿真成这样的结果却是难受,不知道怎么办?

图1: 驱动端;图2、3:接受端

图4:驱动端发出时钟差分波形;

图5、6:接受端收到时钟差分波形。

仿真成这样的结果却是难受,不知道怎么办?

你这些数据只能让大家陪你一起难受啊

唉

你这些数据只能让大家陪你一起难受啊

这是嘛结果啊,真是你这些数据只能让大家陪你一起难受啊

阻抗不匹配造成嚴重反射 , 考慮串上電阻試試看.