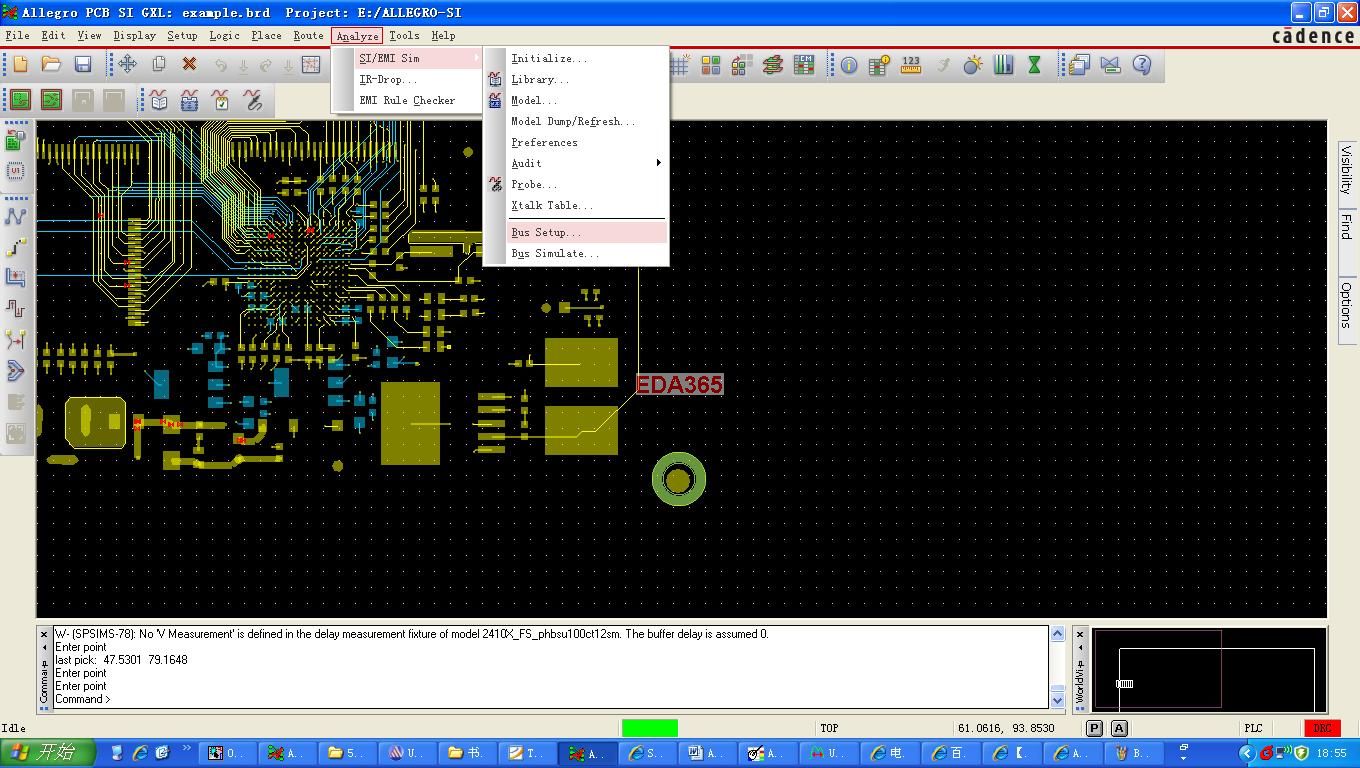

Allegro中bus仿真

时间:10-02

整理:3721RD

点击:

Allegro中bus仿真

却弹出对话框

我把IBIS模型都分配给元器件了,不知弹出对话框是啥意思呢?还有对于DDR2 SDRAM,建立时间和保持时间需要考虑由于信号边沿不单调造成的时序降额。Allegro中做bus仿真时候需要导入derating文件,请教怎样根据datasheet中的derating表格转换成allegro可调用的格式?有网友说Allegro安装目录有例子的吧谢谢在share\pcb\txt路径下可以找到,我没找到啊?从芯片文档能直接得到的建立时间和保持时间的基本要求;tSETUP(derating)和tHOLD(derating)是根据信号及其参考时钟的真实爬升速率查表得出的降额值。Allegro作为软件怎么能计算好呢?据说Hyperlynx8.0能?请教各位高手?谢谢了!

却弹出对话框

This signal model assigned to the components in this bus do not have model selectors defined for the pins of the bus

This means that the default ,model assigned

to each of the bus pins will be used for the driver,receiver and standby states

这个信号模型分配在这路公交车到组件没有对总线的引脚定义的模型选择

这意味着,默认情况下,模型分配到总线引脚都将被驱动程序,接收和待机状态使用

我把IBIS模型都分配给元器件了,不知弹出对话框是啥意思呢?还有对于DDR2 SDRAM,建立时间和保持时间需要考虑由于信号边沿不单调造成的时序降额。Allegro中做bus仿真时候需要导入derating文件,请教怎样根据datasheet中的derating表格转换成allegro可调用的格式?有网友说Allegro安装目录有例子的吧谢谢在share\pcb\txt路径下可以找到,我没找到啊?从芯片文档能直接得到的建立时间和保持时间的基本要求;tSETUP(derating)和tHOLD(derating)是根据信号及其参考时钟的真实爬升速率查表得出的降额值。Allegro作为软件怎么能计算好呢?据说Hyperlynx8.0能?请教各位高手?谢谢了!

那个警告不必理会,只是因为你的model不是以model select形式分配模型的,而是直接分配模型到pin的,所以不用理会。其他的的问题我没做过,希望其他人能帮上你吧

谢谢。我再研究研究,也期待高手解答