PCI总线时序仿真

时间:10-02

整理:3721RD

点击:

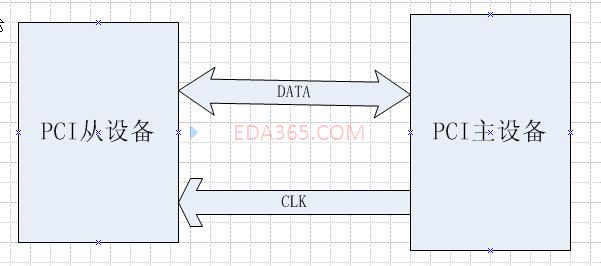

如下图1所示,PCI总线的时钟由主设备内部提供,当PCI设备发动数据传输时,此时的时钟肯定不是源同步,好像也不能说是共同时钟。这种情况下,如何进行时序仿真?

恳请大家指点下,谢谢!

恳请大家指点下,谢谢!

PCI主设备上没有其它的时钟了,是不是有可能PCI主设备芯片内部有一个回环时钟送给自已,进行读操作?

异步时钟考虑,用master端的clock采样slave发过来的数据。

譬如CLK1从Master发出,通过Flight_clock时间到达Slave,然后经过Slave的Tco时间由Slave发出Data,再经过Flight_data时间到达Master。我们就用此时刻master的CLK1沿来采样这个到达的data沿,通常这时需要加上一个时钟周期。

哦,那我明白了。

实在太感谢您了,给予我这么多无私的帮助!

不用客气,互相学习

wakinoda,再请问您一下:

Master端的时钟功能很强大:

1,在Master端打出数据

2,在Slave端锁存数据

3,在Master端发出时钟信号到Slave端打出数据

4,在Master端锁存数据

这样设计合理吗?有必要吗?

谢谢!

其实异步时钟一般都是用在一些时序不大敏感的电路中,这样就不需要太复杂的时钟结构,所以说不是合理或者必要,而是何乐而不为。

哦,那我明白了,呵,多谢了!