HyperLynx 过孔建模不准确?

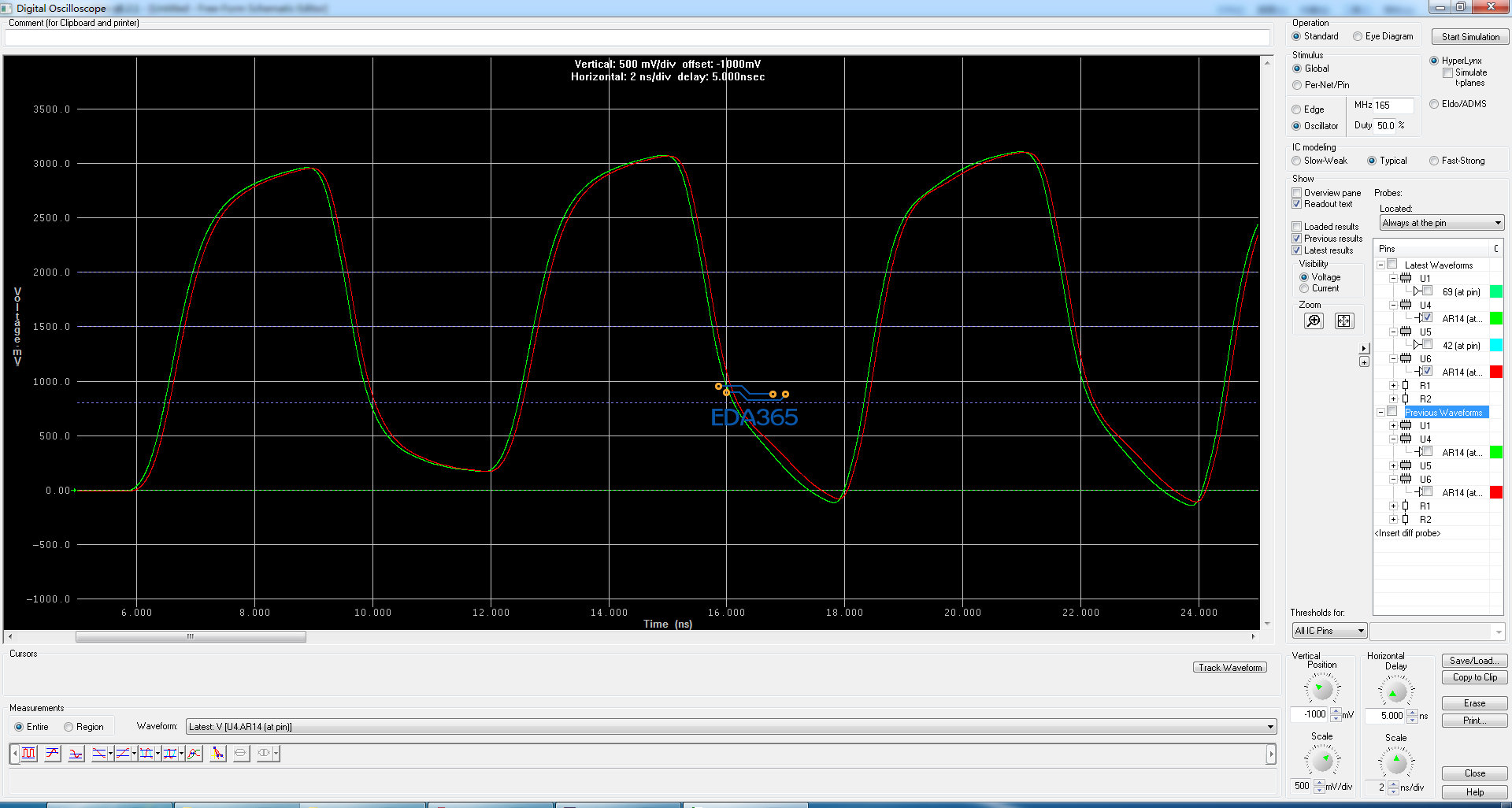

在使用HyperLynx进行LineSim时,对比添加过孔和未添加过孔的传输线路,信号波形相差无几,这是否与实际情况相悖呢?

根据高速电路的设计知识来讲,一般在高速布线时要尽可能的减少过孔数量,因为过孔会对信号完整性产生较大的印象。即使需要添加过孔,某些走线也不能多于3个过孔。但实际的仿真结果却显示过孔对信号的影响不大,实际情况就是如此呢,还是HyperLynx中对于过孔的建模有问题?

还请高手不吝赐教!

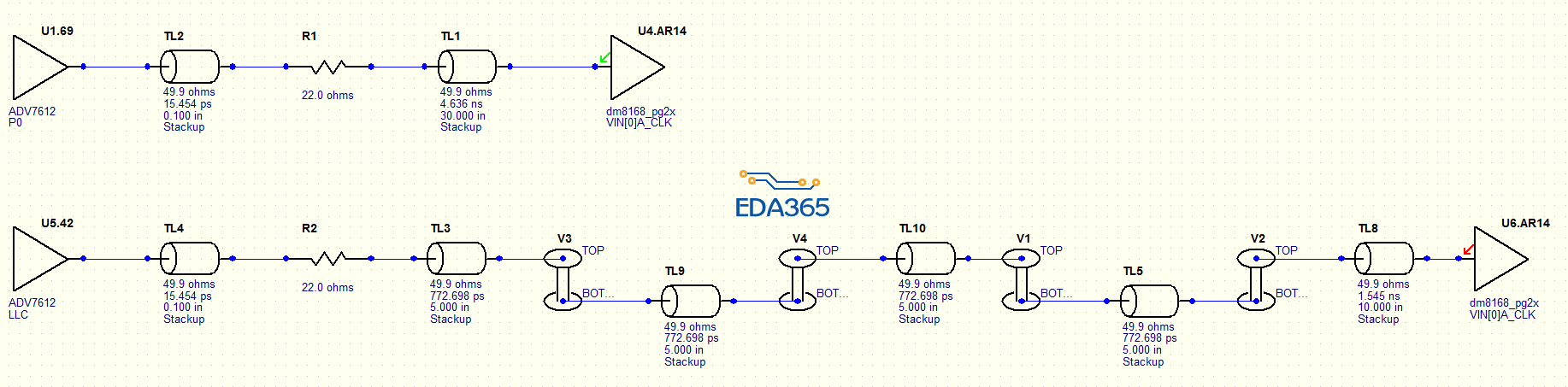

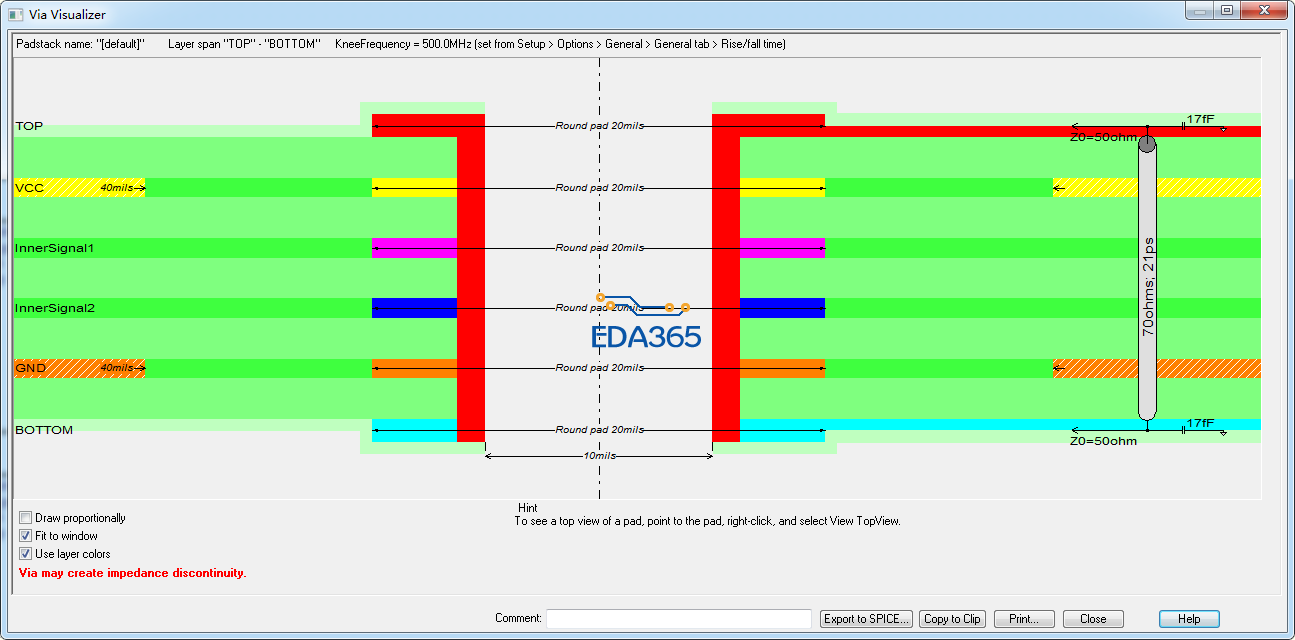

过孔的模型参数

木有人懂吗?

我感兴趣的是,你希望周期大约为6ns,上升时间大约为1ns的周期信号,在过孔处产生什么样的影响?

常用的过孔,一定是在一段带宽范围内对信号影响较小才被确定下来的。

hyperlynx在5G以下的结果还是没有问题的,不要怀疑工具的准确性,搞清楚自己忽略了什么地方。

同意3楼的看法,而且虽然是周期大约6ns,上升时间大约为1ns的周期信号,从波形中也可以看出比较明显的就是已经对时序产生了影响,至于这个影响是不是影响你的channel。那就另说了。

看一下S参数,描到20G,再到差别

之前从很多介绍高速信号Layout的书上得知,一般高速的走线经过过孔的数量都是有限制的,原因就是经过过孔后,会对信号质量产生较大的影响。但经过自己的仿真,添加了4个过孔,而信号却只是有了一点延迟,没有明显的畸变,所以感觉似乎对信号影响没有想象中的大。难道我在设置过孔建模的时候还存在问题,还是本来就应该是这样的结果?

这里没影响是因为我所问的,1ns上升时间的周期信号,带来的寄生效应不足以影响你的信号。

从传输线长度的角度来理解,所有过孔的叠加长度连你上升时间的1/10都不到。

从寄生参数的角度来理解,寄生参数带来的感容突变延时连上升时间的1/10都不到。

所以你希望看到过孔的影响,两个方向,信号上升时间变短或者大量增加信号过孔,至少你过孔的总长度要大于上升时间的1/10。

首先不要怀疑工具基本建模的准确性,至少在1GHz以下的带宽内不要怀疑。多多理解基础理论才是重点。

恩,解释的有深度

借宝贴刷威望!

1.输入输出芯片引脚属性 及所加的信号是否完全相同?

2.22欧姆电阻什么用?

3.激励源信号频率太低,时延的细节没有显现出来

4.由细节 再深入研究过孔的影响(如 阻抗 时延 和过孔模型)

小编威武!